Vivado HLS を使ってみた(その3) [FPGA]

ようやく対象となる関数本体を作ります。「Source」にある「rgb2ycbcr.cpp」を編集します。

まずはテストベンチの関数をそのまんまコピーして、関数名を「rgb2ycbcr」にします。浮動小数点使ってますが、気にしません。

main関数のコメントを切り替えて、この関数を使うように変更します。シミュレーション結果はもちろん変わりません。

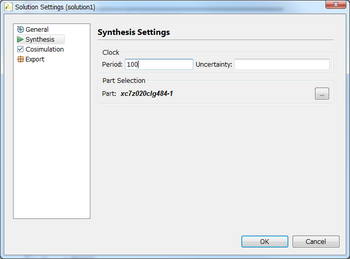

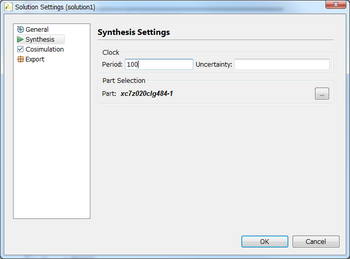

試しにこのまま合成してみます。の前にソリューションの周波数を落とします。これは周波数が高いまま(デフォルト100MHz)だとレポート画面が横長になりすぎるから、というだけの理由です。

緑色の再生ボタン(C Synthesis)を押します。ものの10数秒で完了です。レポートファイルがこちら。

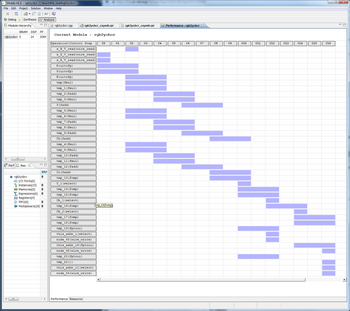

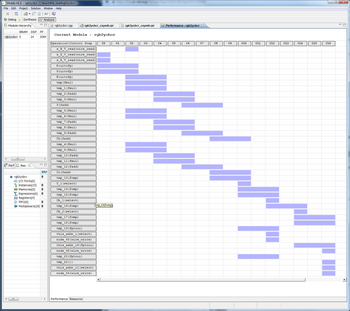

「Analysis」でデータの流れが見られます。

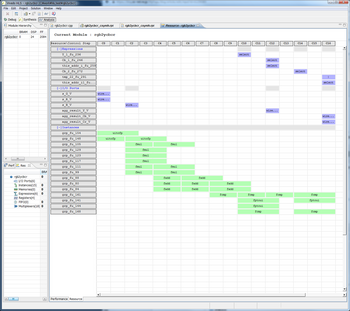

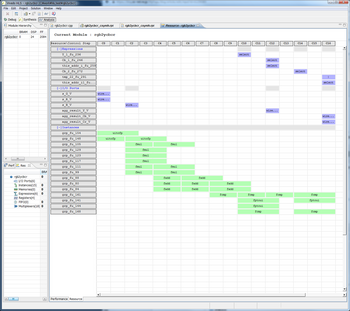

リソースの使われ方。

なにも指示を与えていないので、パイプライン化もされていません。レイテンシ16クロック、17クロックに1演算、となっています。浮動小数点のコアを使っているので結構大きいです、が、これで良いのだったらこのまま完成でもOK?実際にインプリを試してはいませんが、HDLは普通にできてるのでこのままでも大丈夫そうです。

とは言えさすがにナンなので、整数化してみます。

まずはテストベンチの関数をそのまんまコピーして、関数名を「rgb2ycbcr」にします。浮動小数点使ってますが、気にしません。

#include "rgb2ycbcr.h"

#define dat 256 /* pow(2, dw) */

YCbCr rgb2ycbcr(RGB s)

{

YCbCr d;

const float cY [3] = { 0.2126f, 0.7152f, 0.0722f };

const float cCb[3] = {-0.1146f, -0.3854f, 0.5000f };

const float cCr[3] = { 0.5000f, -0.4542f, -0.0458f };

const float op5 = 0.5f * dat;

const float llim = 0.0f;

const float ulim = (float)(dat-1);

float R,G,B;

float Y,Cb,Cr;

R = (float)s.R;

G = (float)s.G;

B = (float)s.B;

Y = cY [0] * R + cY [1] * G + cY [2] * B;

Cb = cCb[0] * R + cCb[1] * G + cCb[2] * B + op5;

Cr = cCr[0] * R + cCr[1] * G + cCr[2] * B + op5;

if (Y < llim) Y = llim; if (ulim < Y ) Y = ulim;

if (Cb < llim) Cb = llim; if (ulim < Cb) Cb = ulim;

if (Cb < llim) Cr = llim; if (ulim < Cb) Cr = ulim;

d.Y = Y;

d.Cb = Cb;

d.Cr = Cr;

return d;

}

main関数のコメントを切り替えて、この関数を使うように変更します。シミュレーション結果はもちろん変わりません。

試しにこのまま合成してみます。の前にソリューションの周波数を落とします。これは周波数が高いまま(デフォルト100MHz)だとレポート画面が横長になりすぎるから、というだけの理由です。

緑色の再生ボタン(C Synthesis)を押します。ものの10数秒で完了です。レポートファイルがこちら。

================================================================

== Vivado HLS Report for 'rgb2ycbcr'

================================================================

* Date:

* Version: 2013.1

* Project: rgb2ycbcr

* Solution: solution1

* Product family: zynq zynq_fpv6

* Target device: xc7z020clg484-1

================================================================

== Performance Estimates

================================================================

+ Timing (ns):

* Summary:

+---------+--------+----------+------------+

| Clock | Target | Estimated| Uncertainty|

+---------+--------+----------+------------+

|default | 100.00| 37.63| 12.50|

+---------+--------+----------+------------+

+ Latency (clock cycles):

* Summary:

+-----+-----+-----+-----+---------+

| Latency | Interval | Pipeline|

| min | max | min | max | Type |

+-----+-----+-----+-----+---------+

| 16| 16| 17| 17| none |

+-----+-----+-----+-----+---------+

+ Detail:

* Instance:

N/A

* Loop:

N/A

================================================================

== Utilization Estimates

================================================================

* Summary:

+-----------------+---------+-------+--------+-------+

| Name | BRAM_18K| DSP48E| FF | LUT |

+-----------------+---------+-------+--------+-------+

|Expression | -| -| 0| 114|

|FIFO | -| -| -| -|

|Instance | -| 24| 2007| 5419|

|Memory | -| -| -| -|

|Multiplexer | -| -| -| 388|

|Register | -| -| 77| -|

|ShiftMemory | -| -| -| -|

+-----------------+---------+-------+--------+-------+

|Total | 0| 24| 2084| 5921|

+-----------------+---------+-------+--------+-------+

|Available | 280| 220| 106400| 53200|

+-----------------+---------+-------+--------+-------+

|Utilization (%) | 0| 10| 1| 11|

+-----------------+---------+-------+--------+-------+

+ Detail:

* Instance:

+-------------------------------------------+----------------------------------------+---------+-------+-----+-----+

| Instance | Module | BRAM_18K| DSP48E| FF | LUT |

+-------------------------------------------+----------------------------------------+---------+-------+-----+-----+

|rgb2ycbcr_fadd_32ns_32ns_32_3_full_dsp_U1 |rgb2ycbcr_fadd_32ns_32ns_32_3_full_dsp | 0| 2| 177| 385|

|rgb2ycbcr_fadd_32ns_32ns_32_3_full_dsp_U2 |rgb2ycbcr_fadd_32ns_32ns_32_3_full_dsp | 0| 2| 177| 385|

|rgb2ycbcr_fadd_32ns_32ns_32_3_full_dsp_U3 |rgb2ycbcr_fadd_32ns_32ns_32_3_full_dsp | 0| 2| 177| 385|

|rgb2ycbcr_fcmp_32ns_32ns_1_3_U14 |rgb2ycbcr_fcmp_32ns_32ns_1_3 | 0| 0| 66| 239|

|rgb2ycbcr_fcmp_32ns_32ns_1_3_U15 |rgb2ycbcr_fcmp_32ns_32ns_1_3 | 0| 0| 66| 239|

|rgb2ycbcr_fmul_32ns_32ns_32_3_max_dsp_U4 |rgb2ycbcr_fmul_32ns_32ns_32_3_max_dsp | 0| 3| 128| 320|

|rgb2ycbcr_fmul_32ns_32ns_32_3_max_dsp_U5 |rgb2ycbcr_fmul_32ns_32ns_32_3_max_dsp | 0| 3| 128| 320|

|rgb2ycbcr_fmul_32ns_32ns_32_3_max_dsp_U6 |rgb2ycbcr_fmul_32ns_32ns_32_3_max_dsp | 0| 3| 128| 320|

|rgb2ycbcr_fmul_32ns_32ns_32_3_max_dsp_U7 |rgb2ycbcr_fmul_32ns_32ns_32_3_max_dsp | 0| 3| 128| 320|

|rgb2ycbcr_fmul_32ns_32ns_32_3_max_dsp_U8 |rgb2ycbcr_fmul_32ns_32ns_32_3_max_dsp | 0| 3| 128| 320|

|rgb2ycbcr_fmul_32ns_32ns_32_3_max_dsp_U9 |rgb2ycbcr_fmul_32ns_32ns_32_3_max_dsp | 0| 3| 128| 320|

|rgb2ycbcr_fptoui_32ns_64_3_U10 |rgb2ycbcr_fptoui_32ns_64_3 | 0| 0| 160| 414|

|rgb2ycbcr_fptoui_32ns_64_3_U11 |rgb2ycbcr_fptoui_32ns_64_3 | 0| 0| 160| 414|

|rgb2ycbcr_uitofp_64ns_32_3_U12 |rgb2ycbcr_uitofp_64ns_32_3 | 0| 0| 128| 519|

|rgb2ycbcr_uitofp_64ns_32_3_U13 |rgb2ycbcr_uitofp_64ns_32_3 | 0| 0| 128| 519|

+-------------------------------------------+----------------------------------------+---------+-------+-----+-----+

|Total | | 0| 24| 2007| 5419|

+-------------------------------------------+----------------------------------------+---------+-------+-----+-----+

* Memory:

N/A

* FIFO:

N/A

* Shift register:

N/A

* Expression:

+------------------+----------+-------+---+----+------------+------------+

| Variable Name | Operation| DSP48E| FF| LUT| Bitwidth P0| Bitwidth P1|

+------------------+----------+-------+---+----+------------+------------+

|Cb_1_fu_246_p3 | Select | 0| 0| 32| 1| 1|

|Cb_2_fu_272_p3 | Select | 0| 0| 32| 1| 31|

|Y_1_fu_236_p3 | Select | 0| 0| 32| 1| 1|

|agg_result_Cr_V | Select | 0| 0| 8| 1| 8|

|agg_result_Y_V | Select | 0| 0| 8| 1| 2|

|tmp_22_fu_291_p2 | or | 0| 0| 2| 1| 1|

+------------------+----------+-------+---+----+------------+------------+

|Total | | 0| 0| 114| 6| 44|

+------------------+----------+-------+---+----+------------+------------+

* Multiplexer:

+-------------------+----+-----------+-----+-----------+

| Name | LUT| Input Size| Bits| Total Bits|

+-------------------+----+-----------+-----+-----------+

|grp_fu_105_p0 | 32| 2| 32| 64|

|grp_fu_105_p1 | 13| 2| 13| 26|

|grp_fu_111_p1 | 10| 2| 10| 20|

|grp_fu_141_p0 | 32| 2| 32| 64|

|grp_fu_148_p0 | 8| 2| 8| 16|

|grp_fu_161_opcode | 2| 2| 2| 4|

|grp_fu_161_p0 | 32| 4| 32| 128|

|grp_fu_161_p1 | 10| 2| 10| 20|

|grp_fu_168_opcode | 2| 2| 2| 4|

|grp_fu_168_p0 | 32| 2| 32| 64|

|grp_fu_168_p1 | 10| 2| 10| 20|

|grp_fu_80_p0 | 32| 3| 32| 96|

|grp_fu_80_p1 | 32| 3| 32| 96|

|grp_fu_84_p0 | 32| 3| 32| 96|

|grp_fu_84_p1 | 32| 3| 32| 96|

|grp_fu_88_p0 | 32| 2| 32| 64|

|grp_fu_88_p1 | 32| 2| 32| 64|

|grp_fu_99_p1 | 13| 2| 13| 26|

+-------------------+----+-----------+-----+-----------+

|Total | 388| 42| 388| 968|

+-------------------+----+-----------+-----+-----------+

* Register:

+----------------+----+-----+-----------+

| Name | FF | Bits| Const Bits|

+----------------+----+-----+-----------+

|Cb_1_reg_348 | 32| 32| 0|

|ap_CS_fsm | 5| 5| 0|

|reg_201 | 32| 32| 0|

|tmp_25_reg_354 | 8| 8| 0|

+----------------+----+-----+-----------+

|Total | 77| 77| 0|

+----------------+----+-----+-----------+

================================================================

== Interface

================================================================

* Summary:

+------------------------+-----+-----+------------+-----------------+--------------+

| RTL Ports | Dir | Bits| Protocol | Source Object | C Type |

+------------------------+-----+-----+------------+-----------------+--------------+

|ap_clk | in | 1| ap_ctrl_hs | rgb2ycbcr | return value |

|ap_rst | in | 1| ap_ctrl_hs | rgb2ycbcr | return value |

|ap_start | in | 1| ap_ctrl_hs | rgb2ycbcr | return value |

|ap_done | out | 1| ap_ctrl_hs | rgb2ycbcr | return value |

|ap_idle | out | 1| ap_ctrl_hs | rgb2ycbcr | return value |

|ap_ready | out | 1| ap_ctrl_hs | rgb2ycbcr | return value |

|agg_result_Y_V | out | 8| ap_vld | agg_result_Y_V | pointer |

|agg_result_Y_V_ap_vld | out | 1| ap_vld | agg_result_Y_V | pointer |

|agg_result_Cb_V | out | 8| ap_vld | agg_result_Cb_V | pointer |

|agg_result_Cb_V_ap_vld | out | 1| ap_vld | agg_result_Cb_V | pointer |

|agg_result_Cr_V | out | 8| ap_vld | agg_result_Cr_V | pointer |

|agg_result_Cr_V_ap_vld | out | 1| ap_vld | agg_result_Cr_V | pointer |

|s_R_V | in | 8| ap_none | s_R_V | scalar |

|s_G_V | in | 8| ap_none | s_G_V | scalar |

|s_B_V | in | 8| ap_none | s_B_V | scalar |

+------------------------+-----+-----+------------+-----------------+--------------+

「Analysis」でデータの流れが見られます。

リソースの使われ方。

なにも指示を与えていないので、パイプライン化もされていません。レイテンシ16クロック、17クロックに1演算、となっています。浮動小数点のコアを使っているので結構大きいです、が、これで良いのだったらこのまま完成でもOK?実際にインプリを試してはいませんが、HDLは普通にできてるのでこのままでも大丈夫そうです。

とは言えさすがにナンなので、整数化してみます。

2013-04-24 18:42

nice!(0)

コメント(0)

トラックバック(0)

コメント 0