AXIの勉強(その2.1) [AXI]

続いてリードの依存関係。

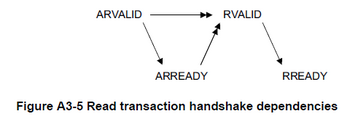

Read transaction dependencies

1• the master must not wait for the slave to assert ARREADY before asserting ARVALID

2• the slave can wait for ARVALID to be asserted before it asserts ARREADY

3• the slave can assert ARREADY before ARVALID is asserted

4• the slave must wait for both ARVALID and ARREADY to be asserted before it asserts RVALID to indicate that valid data is available

5• the slave must not wait for the master to assert RREADY before asserting RVALID

6• the master can wait for RVALID to be asserted before it asserts RREADY

7• the master can assert RREADY before RVALID is asserted.

なんかいっぱいありますが、分けてみるとわかりやすいかと思います。

まず上3つ。1,2,3。

・マスターのARVALIDは、ARREADYに依存してはならない

・スレーブはARVALIDを待ってからARREADYをアサートしても良い

・スレーブはARVALIDより前にARREADYをアサートしても良い

前の記事のソース・シンクの関係と同じです。ARチャンネルのデッドロックを防止する制約です。

下3つ。5,6,7。

・スレーブのRVALIDは、RREADYに依存してはならない

・マスターはRVALIDを待ってからRREADYをアサートしても良い

・マスターはRVALIDより前にRREADYをアサートしても良い

Rチャンネルのデッドロック防止です。

真ん中の一つ。4。

・スレーブはARREADYとARVALID両方がアサートされるのを待ってからRVALIDをアサートすること

ARREADYとARVALID両方がアサートされるということは、ARの転送が完了したということです。

ARVALIDはマスターがドライブしているので、スレーブ側のRのソースシーケンサーの制約になります。つまり、

・スレーブはARVALIDが来ないうちにRVALIDをアサートしてはならない

・スレーブはARREADYを先に返してからRVALIDをアサートすること

という制約です。

要は

・アドレス情報が与えられてもいないのに余計な情報を勝手に送るな

・アドレス情報を受け取ったことを、まずマスターに知らせてから、データを返せ

という制約です。1つ目はまあ良いですよね。

2つ目、例えばスレーブがARREADYを返さずに、ARの情報をゆっくり解析する回路にしたとします。これ自体は正しい動作です。

if (ARVALID) then

1クロック目:AR.addr評価

2クロック目:AR.length評価

3クロック目:

・・・・

nクロック目:ARREADY <= '1';

この途中でデータを返すのを違反としています。

if (ARVALID) then

1クロック目:AR.addr評価

2クロック目:AR.length評価

3クロック目:RVALID <= '1'; 違反

4クロック目:if (RREADY) then ここでデッドロック

・・・・

nクロック目:ARREADY <= '1';

なぜか。

例えばこれにつながるマスターがこんな風に順番に処理する回路の場合です。あり得る回路です。

アドレス処理ステート

ARVALID <= '1';

↑クロック

if (ARREADY = '1') then ここでデッドロック

ARVALID <= '0';

データ処理ステート

if (ARVALID = '1') then

RREADY <= '1'

・マスターのARシーケンサーがARREADYを確認してからデータの受信処理を行う

・スレーブのRシーケンサーがARREADYをアサートする前にRREADYの評価を行う

この2つがつながるとデッドロックします。

実際の犯人はRREADYを評価していることで、RVALIDをアサートしたこと自体ではないですが。RVALIDを操作したということは、スレーブがデータ処理ステートに入ったことを意味します。けどマスターがアドレス処理のステートのままだと、RREADYが返ってこないかも知れません。

この、スレーブがデータ処理ステートに入ったのに、マスターがアドレス処理ステートのところで止まったまま、となるのを防ぐための制約で、マスター・スレーブともアドレス処理ステートを完了させてからデータ処理ステートに移行しましょう、そのために、スレーブはARREADYを先に返してからRVALIDをアサートすること、という決まり事です。

下のような違反の回路、AXIに慣れてないうちだと、意外と作りがちな回路です。

ARVALIDをアドレスストローブ信号、ARREADYをウェイト制御信号、と認識してるとこんな回路になります。パケット式じゃない、普通のタイミング方式のバスに慣れてる人がはまりやすいパターンです。

AXIはただのインターフェースの仕様で、どんなコーディングしてるのかわからない相手が接続されます。デッドロックのパターンを決めておかないとエラいことになります。なので、こんな制約が存在します。

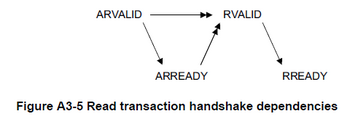

Read transaction dependencies

1• the master must not wait for the slave to assert ARREADY before asserting ARVALID

2• the slave can wait for ARVALID to be asserted before it asserts ARREADY

3• the slave can assert ARREADY before ARVALID is asserted

4• the slave must wait for both ARVALID and ARREADY to be asserted before it asserts RVALID to indicate that valid data is available

5• the slave must not wait for the master to assert RREADY before asserting RVALID

6• the master can wait for RVALID to be asserted before it asserts RREADY

7• the master can assert RREADY before RVALID is asserted.

なんかいっぱいありますが、分けてみるとわかりやすいかと思います。

まず上3つ。1,2,3。

・マスターのARVALIDは、ARREADYに依存してはならない

・スレーブはARVALIDを待ってからARREADYをアサートしても良い

・スレーブはARVALIDより前にARREADYをアサートしても良い

前の記事のソース・シンクの関係と同じです。ARチャンネルのデッドロックを防止する制約です。

下3つ。5,6,7。

・スレーブのRVALIDは、RREADYに依存してはならない

・マスターはRVALIDを待ってからRREADYをアサートしても良い

・マスターはRVALIDより前にRREADYをアサートしても良い

Rチャンネルのデッドロック防止です。

真ん中の一つ。4。

・スレーブはARREADYとARVALID両方がアサートされるのを待ってからRVALIDをアサートすること

ARREADYとARVALID両方がアサートされるということは、ARの転送が完了したということです。

ARVALIDはマスターがドライブしているので、スレーブ側のRのソースシーケンサーの制約になります。つまり、

・スレーブはARVALIDが来ないうちにRVALIDをアサートしてはならない

・スレーブはARREADYを先に返してからRVALIDをアサートすること

という制約です。

要は

・アドレス情報が与えられてもいないのに余計な情報を勝手に送るな

・アドレス情報を受け取ったことを、まずマスターに知らせてから、データを返せ

という制約です。1つ目はまあ良いですよね。

2つ目、例えばスレーブがARREADYを返さずに、ARの情報をゆっくり解析する回路にしたとします。これ自体は正しい動作です。

if (ARVALID) then

1クロック目:AR.addr評価

2クロック目:AR.length評価

3クロック目:

・・・・

nクロック目:ARREADY <= '1';

この途中でデータを返すのを違反としています。

if (ARVALID) then

1クロック目:AR.addr評価

2クロック目:AR.length評価

3クロック目:RVALID <= '1'; 違反

4クロック目:if (RREADY) then ここでデッドロック

・・・・

nクロック目:ARREADY <= '1';

なぜか。

例えばこれにつながるマスターがこんな風に順番に処理する回路の場合です。あり得る回路です。

アドレス処理ステート

ARVALID <= '1';

↑クロック

if (ARREADY = '1') then ここでデッドロック

ARVALID <= '0';

データ処理ステート

if (ARVALID = '1') then

RREADY <= '1'

・マスターのARシーケンサーがARREADYを確認してからデータの受信処理を行う

・スレーブのRシーケンサーがARREADYをアサートする前にRREADYの評価を行う

この2つがつながるとデッドロックします。

実際の犯人はRREADYを評価していることで、RVALIDをアサートしたこと自体ではないですが。RVALIDを操作したということは、スレーブがデータ処理ステートに入ったことを意味します。けどマスターがアドレス処理のステートのままだと、RREADYが返ってこないかも知れません。

この、スレーブがデータ処理ステートに入ったのに、マスターがアドレス処理ステートのところで止まったまま、となるのを防ぐための制約で、マスター・スレーブともアドレス処理ステートを完了させてからデータ処理ステートに移行しましょう、そのために、スレーブはARREADYを先に返してからRVALIDをアサートすること、という決まり事です。

下のような違反の回路、AXIに慣れてないうちだと、意外と作りがちな回路です。

ARVALIDをアドレスストローブ信号、ARREADYをウェイト制御信号、と認識してるとこんな回路になります。パケット式じゃない、普通のタイミング方式のバスに慣れてる人がはまりやすいパターンです。

AXIはただのインターフェースの仕様で、どんなコーディングしてるのかわからない相手が接続されます。デッドロックのパターンを決めておかないとエラいことになります。なので、こんな制約が存在します。

2016-09-17 10:44

nice!(0)

コメント(0)

トラックバック(0)

コメント 0