Vivado HLS を使ってみた(その1) [FPGA]

またご無沙汰です。

最近、ZedBoardとこれ

http://avnet.co.jp/design/kits/xilinx/AES-FMC-IMAGEON-V2000C-G.aspx

入手しました。OnSemiのこのセンサーはFullHD 100fpsというセンサーですが、256x256 1700fpsで使ってみたいです。ちょっとした中速度撮影カメラですね。BayerパターンのRAW出力なので後処理は必要です。

また、Allowから低価格CycloneV SOCのSoCKitが発表されました。

http://www.arrownac.com/solutions/sockit/

DDR3がARMコアとFPGAハードマクロに1GBずつ2系統ってことでしょうか。DS5の扱いがどうなるかによりますが使ってみたいです。HSMCに上記のイメージセンサーつなぎたいな~

まぁ、この辺はおいおい。

さて、これまた最近、Xilinx VivadoのHLSに触れる機会がありました。その昔AutoESLと呼ばれてたC/C++→HDLツールです。もっと効率よい方法があるかもしれませんが、試行錯誤しながら使ってみます。参考資料はこれ。

http://www.xilinx.com/support/documentation/sw_manuals/xilinx2012_2/ug902-vivado-high-level-synthesis.pdf (PDF)

あと、サンプル記述の例が埋め込まれているので、それも参考になります。

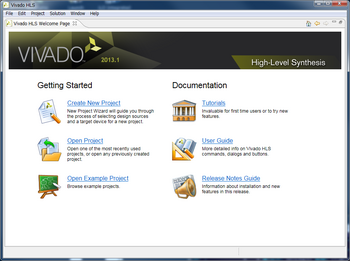

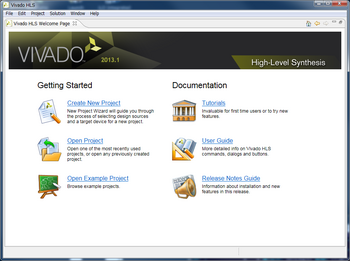

起動画面。

「Create New Project」で新しくプロジェクト作成します。

題材としてRGB→YCbCr変換。IPはどこにでもあるので自分で作る必要は無いんですが、結果がわかっているので試すにはよろしかろうと。

ソースファイルの追加。「Top Function」で指定した関数から下がハードウェアに変換されます。

ここでちょっと違和感。ファイルを追加しないと次にいけないんですが、まだプロジェクトフォルダが作成されていないので、ファイルの場所が?今回の場合

c:\work\hls_test\rgb2ycbcr

フォルダにファイルを入れるような気がするんですが、この時点で「rgb2ycbcr」は無いため、「hls_test」に作ることになります。後でファイルの場所を変えれば良いだけですが…想定されてる使い方が違うのかな?

テストベンチ。あとで。

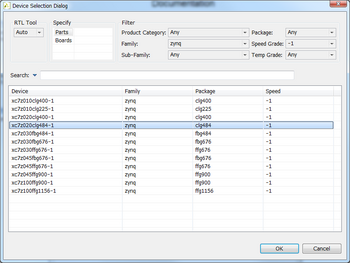

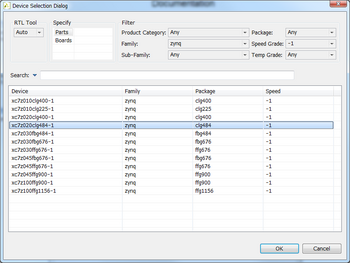

「ソリューション」と呼ばれる、回路生成の設定画面。

コンパイラオプションセットみたいな感じです。速度とかデバイスを指定します。これは後で変更可能ですし、複数のソリューションを用意することもできます。

今回はZedBoardを想定してZynq7020を設定。速度はデフォルト。

設定後。あ、デバイス間違えてるw

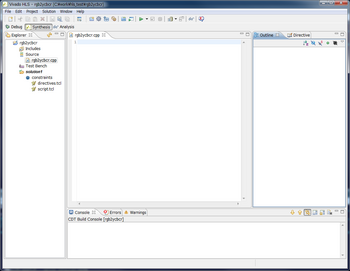

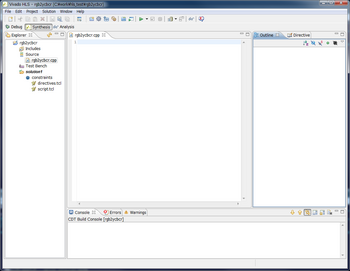

設定完了後の画面。ここにテストベンチとか追加して行きます。

使い方はほぼEclipseのままです。

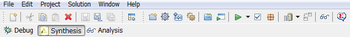

上のメニューとかボタン。

緑の再生ボタンがHDL生成。その左がC/C++シミュレーション。この二つをよく使います。

Debug、Synthesis、Analysisはパースペクティブの切り替え。Debugは普通のCデバッガです。Analysisがハードウェアのデータの流れを解析するツールになります。

ここからソースを記述していきます。順番として

・テストベンチ作成。リファレンスとなるデータの読み書きを行うプログラムを書きます。

・ハードウェアになる対象の関数を作成。

・対象の関数を最適化。しなくても良いかも。

・ディレクティブ(指示子?)追加。I/Oの種類とかパイプラインとか。

てな感じで行きます。

最近、ZedBoardとこれ

http://avnet.co.jp/design/kits/xilinx/AES-FMC-IMAGEON-V2000C-G.aspx

入手しました。OnSemiのこのセンサーはFullHD 100fpsというセンサーですが、256x256 1700fpsで使ってみたいです。ちょっとした中速度撮影カメラですね。BayerパターンのRAW出力なので後処理は必要です。

また、Allowから低価格CycloneV SOCのSoCKitが発表されました。

http://www.arrownac.com/solutions/sockit/

DDR3がARMコアとFPGAハードマクロに1GBずつ2系統ってことでしょうか。DS5の扱いがどうなるかによりますが使ってみたいです。HSMCに上記のイメージセンサーつなぎたいな~

まぁ、この辺はおいおい。

さて、これまた最近、Xilinx VivadoのHLSに触れる機会がありました。その昔AutoESLと呼ばれてたC/C++→HDLツールです。もっと効率よい方法があるかもしれませんが、試行錯誤しながら使ってみます。参考資料はこれ。

http://www.xilinx.com/support/documentation/sw_manuals/xilinx2012_2/ug902-vivado-high-level-synthesis.pdf (PDF)

あと、サンプル記述の例が埋め込まれているので、それも参考になります。

起動画面。

「Create New Project」で新しくプロジェクト作成します。

題材としてRGB→YCbCr変換。IPはどこにでもあるので自分で作る必要は無いんですが、結果がわかっているので試すにはよろしかろうと。

ソースファイルの追加。「Top Function」で指定した関数から下がハードウェアに変換されます。

ここでちょっと違和感。ファイルを追加しないと次にいけないんですが、まだプロジェクトフォルダが作成されていないので、ファイルの場所が?今回の場合

c:\work\hls_test\rgb2ycbcr

フォルダにファイルを入れるような気がするんですが、この時点で「rgb2ycbcr」は無いため、「hls_test」に作ることになります。後でファイルの場所を変えれば良いだけですが…想定されてる使い方が違うのかな?

テストベンチ。あとで。

「ソリューション」と呼ばれる、回路生成の設定画面。

コンパイラオプションセットみたいな感じです。速度とかデバイスを指定します。これは後で変更可能ですし、複数のソリューションを用意することもできます。

今回はZedBoardを想定してZynq7020を設定。速度はデフォルト。

設定後。あ、デバイス間違えてるw

設定完了後の画面。ここにテストベンチとか追加して行きます。

使い方はほぼEclipseのままです。

上のメニューとかボタン。

緑の再生ボタンがHDL生成。その左がC/C++シミュレーション。この二つをよく使います。

Debug、Synthesis、Analysisはパースペクティブの切り替え。Debugは普通のCデバッガです。Analysisがハードウェアのデータの流れを解析するツールになります。

ここからソースを記述していきます。順番として

・テストベンチ作成。リファレンスとなるデータの読み書きを行うプログラムを書きます。

・ハードウェアになる対象の関数を作成。

・対象の関数を最適化。しなくても良いかも。

・ディレクティブ(指示子?)追加。I/Oの種類とかパイプラインとか。

てな感じで行きます。

2013-04-24 16:57

nice!(0)

コメント(0)

トラックバック(0)

コメント 0