ZedBoard Linux (5) [FPGA]

Linux管理外のメモリ空間がホントに思ったとおりになってるのか、FPGAから読み書きしてみます。

接続方法ですが、諸事情(笑)によりAXI3。

…はじめの頃はAXI4ににしてpcore形式で登録したりもしてたのですが、最近はハードマクロのAXI-HP0~3を直接外に出してそこにつなぐパターンが多くなってます。作る時に毎回XPS立ち上げてうんたらかんたらやるのが面倒に感じてしまい、まずはAXIを外に出してXPSの作業はおしまい、後は外で作成、って感じです。この場合、ハードマクロのインターフェースは、AXI4ではなくAXI3+QoSです。pcore形式でつなぐ場合はAXI4~AXI3変換が自動的に追加されてます。

AlteraのSOPC Builder、Qsysでは面倒に感じず、そのまま作業することが多いんですよね。なにかセンスが違うんでしょう。ARMの付いたSoCシリーズは使ったこと無いのでわかりませんが…VivadoのIPインテグレーターがどうかもまだ試していません。

ということで、FPGA側のAXIマスターはAXI3になります。スレーブはレジスタの読み書きぐらいしかしないので、AXI~APBブリッジのIPを使ってしまいます。手抜き手抜き。

ちなみにAXIの3と4の違いは中の情報(パケット、プロトコル)の違いであって、タイミングは変わりません(依存関係に追加規定はあります)。簡単なAXIマスターモジュールで関係するのはバースト長(AXI3:4bit:最大16回、AXI4:8bit:最大256回)ぐらいじゃないですかね?

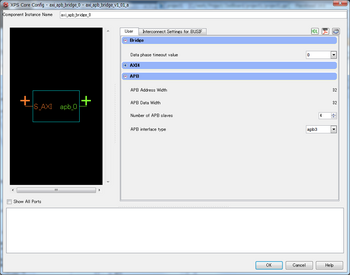

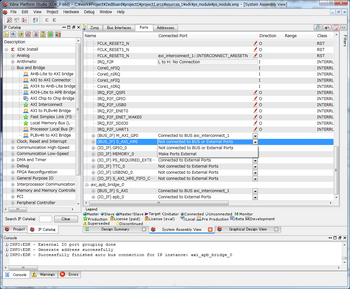

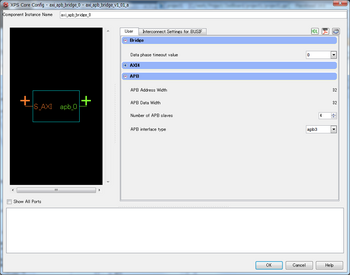

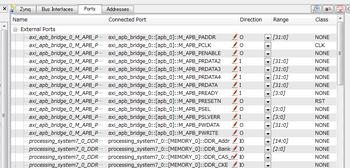

XPSの作業。まずはAXI-APBブリッジを追加します。

APBのスレーブ本数は適当に4本。

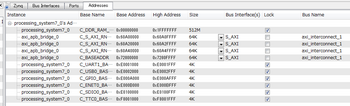

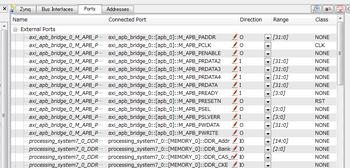

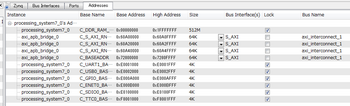

自動的にアドレスが割り当てられ、外部にポートが出ます。

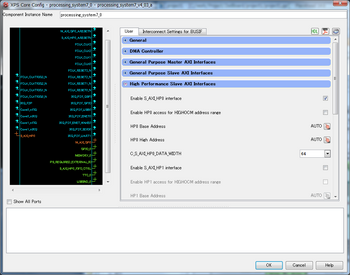

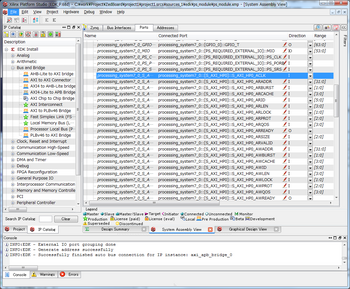

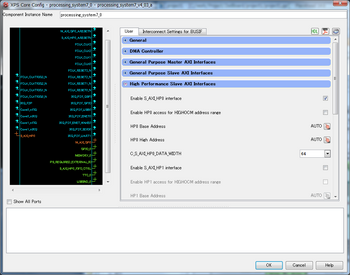

PSセッティングの画面からHigh Performance AXIをクリックし、設定画面からS_AXI_HP0を有効に。

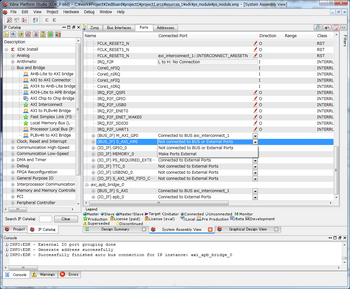

最初はどこにも接続されてないので、Portタブから「S_AXI_HP0」を「Make Ports External」にします。

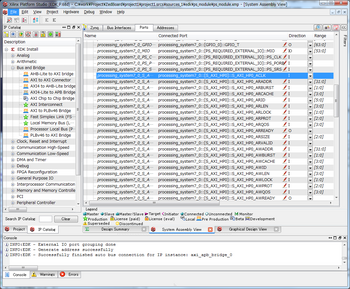

「S_AXI_HP0」が直接外部ポートに出てきます。

※「S_AXI_HP0_ACLK」が入力な点に注意。AXI_HPはFIFOになっていて、クロックを自由に設定できます。他のAXIもクロックブリッジが付いてます。

こうしてできた_stub.vがこちら。

XPSの作業は終了。後は普通にロジック作るだけです。

接続方法ですが、諸事情(笑)によりAXI3。

…はじめの頃はAXI4ににしてpcore形式で登録したりもしてたのですが、最近はハードマクロのAXI-HP0~3を直接外に出してそこにつなぐパターンが多くなってます。作る時に毎回XPS立ち上げてうんたらかんたらやるのが面倒に感じてしまい、まずはAXIを外に出してXPSの作業はおしまい、後は外で作成、って感じです。この場合、ハードマクロのインターフェースは、AXI4ではなくAXI3+QoSです。pcore形式でつなぐ場合はAXI4~AXI3変換が自動的に追加されてます。

AlteraのSOPC Builder、Qsysでは面倒に感じず、そのまま作業することが多いんですよね。なにかセンスが違うんでしょう。ARMの付いたSoCシリーズは使ったこと無いのでわかりませんが…VivadoのIPインテグレーターがどうかもまだ試していません。

ということで、FPGA側のAXIマスターはAXI3になります。スレーブはレジスタの読み書きぐらいしかしないので、AXI~APBブリッジのIPを使ってしまいます。手抜き手抜き。

ちなみにAXIの3と4の違いは中の情報(パケット、プロトコル)の違いであって、タイミングは変わりません(依存関係に追加規定はあります)。簡単なAXIマスターモジュールで関係するのはバースト長(AXI3:4bit:最大16回、AXI4:8bit:最大256回)ぐらいじゃないですかね?

XPSの作業。まずはAXI-APBブリッジを追加します。

APBのスレーブ本数は適当に4本。

自動的にアドレスが割り当てられ、外部にポートが出ます。

PSセッティングの画面からHigh Performance AXIをクリックし、設定画面からS_AXI_HP0を有効に。

最初はどこにも接続されてないので、Portタブから「S_AXI_HP0」を「Make Ports External」にします。

「S_AXI_HP0」が直接外部ポートに出てきます。

※「S_AXI_HP0_ACLK」が入力な点に注意。AXI_HPはFIFOになっていて、クロックを自由に設定できます。他のAXIもクロックブリッジが付いてます。

こうしてできた_stub.vがこちら。

//-----------------------------------------------------------------------------

// ps_module_stub.v

//-----------------------------------------------------------------------------

module ps_module_stub

(

processing_system7_0_MIO,

processing_system7_0_PS_SRSTB_pin,

processing_system7_0_PS_CLK_pin,

processing_system7_0_PS_PORB_pin,

processing_system7_0_DDR_Clk,

processing_system7_0_DDR_Clk_n,

processing_system7_0_DDR_CKE,

processing_system7_0_DDR_CS_n,

processing_system7_0_DDR_RAS_n,

processing_system7_0_DDR_CAS_n,

processing_system7_0_DDR_WEB_pin,

processing_system7_0_DDR_BankAddr,

processing_system7_0_DDR_Addr,

processing_system7_0_DDR_ODT,

processing_system7_0_DDR_DRSTB,

processing_system7_0_DDR_DQ,

processing_system7_0_DDR_DM,

processing_system7_0_DDR_DQS,

processing_system7_0_DDR_DQS_n,

processing_system7_0_DDR_VRN,

processing_system7_0_DDR_VRP,

processing_system7_0_GPIO_I_pin,

processing_system7_0_GPIO_O_pin,

processing_system7_0_GPIO_T_pin,

processing_system7_0_FCLK_CLK0_pin,

processing_system7_0_FCLK_CLK1_pin,

processing_system7_0_FCLK_CLK2_pin,

processing_system7_0_FCLK_CLK3_pin,

axi_apb_bridge_0_M_APB_PCLK_pin,

axi_apb_bridge_0_M_APB_PRESETN_pin,

axi_apb_bridge_0_M_APB_PADDR_pin,

axi_apb_bridge_0_M_APB_PSEL_pin,

axi_apb_bridge_0_M_APB_PENABLE_pin,

axi_apb_bridge_0_M_APB_PWRITE_pin,

axi_apb_bridge_0_M_APB_PWDATA_pin,

axi_apb_bridge_0_M_APB_PREADY_pin,

axi_apb_bridge_0_M_APB_PRDATA_pin,

axi_apb_bridge_0_M_APB_PRDATA2_pin,

axi_apb_bridge_0_M_APB_PRDATA3_pin,

axi_apb_bridge_0_M_APB_PRDATA4_pin,

axi_apb_bridge_0_M_APB_PSLVERR_pin,

processing_system7_0_S_AXI_HP0_ARREADY_pin,

processing_system7_0_S_AXI_HP0_AWREADY_pin,

processing_system7_0_S_AXI_HP0_BVALID_pin,

processing_system7_0_S_AXI_HP0_RLAST_pin,

processing_system7_0_S_AXI_HP0_RVALID_pin,

processing_system7_0_S_AXI_HP0_WREADY_pin,

processing_system7_0_S_AXI_HP0_BRESP_pin,

processing_system7_0_S_AXI_HP0_RRESP_pin,

processing_system7_0_S_AXI_HP0_BID_pin,

processing_system7_0_S_AXI_HP0_RID_pin,

processing_system7_0_S_AXI_HP0_RDATA_pin,

processing_system7_0_S_AXI_HP0_ACLK_pin,

processing_system7_0_S_AXI_HP0_ARVALID_pin,

processing_system7_0_S_AXI_HP0_AWVALID_pin,

processing_system7_0_S_AXI_HP0_BREADY_pin,

processing_system7_0_S_AXI_HP0_RREADY_pin,

processing_system7_0_S_AXI_HP0_WLAST_pin,

processing_system7_0_S_AXI_HP0_WVALID_pin,

processing_system7_0_S_AXI_HP0_ARBURST_pin,

processing_system7_0_S_AXI_HP0_ARLOCK_pin,

processing_system7_0_S_AXI_HP0_ARSIZE_pin,

processing_system7_0_S_AXI_HP0_AWBURST_pin,

processing_system7_0_S_AXI_HP0_AWLOCK_pin,

processing_system7_0_S_AXI_HP0_AWSIZE_pin,

processing_system7_0_S_AXI_HP0_ARPROT_pin,

processing_system7_0_S_AXI_HP0_AWPROT_pin,

processing_system7_0_S_AXI_HP0_ARADDR_pin,

processing_system7_0_S_AXI_HP0_AWADDR_pin,

processing_system7_0_S_AXI_HP0_ARCACHE_pin,

processing_system7_0_S_AXI_HP0_ARLEN_pin,

processing_system7_0_S_AXI_HP0_ARQOS_pin,

processing_system7_0_S_AXI_HP0_AWCACHE_pin,

processing_system7_0_S_AXI_HP0_AWLEN_pin,

processing_system7_0_S_AXI_HP0_AWQOS_pin,

processing_system7_0_S_AXI_HP0_ARID_pin,

processing_system7_0_S_AXI_HP0_AWID_pin,

processing_system7_0_S_AXI_HP0_WID_pin,

processing_system7_0_S_AXI_HP0_WDATA_pin,

processing_system7_0_S_AXI_HP0_WSTRB_pin

);

inout [53:0] processing_system7_0_MIO;

input processing_system7_0_PS_SRSTB_pin;

input processing_system7_0_PS_CLK_pin;

input processing_system7_0_PS_PORB_pin;

inout processing_system7_0_DDR_Clk;

inout processing_system7_0_DDR_Clk_n;

inout processing_system7_0_DDR_CKE;

inout processing_system7_0_DDR_CS_n;

inout processing_system7_0_DDR_RAS_n;

inout processing_system7_0_DDR_CAS_n;

output processing_system7_0_DDR_WEB_pin;

inout [2:0] processing_system7_0_DDR_BankAddr;

inout [14:0] processing_system7_0_DDR_Addr;

inout processing_system7_0_DDR_ODT;

inout processing_system7_0_DDR_DRSTB;

inout [31:0] processing_system7_0_DDR_DQ;

inout [3:0] processing_system7_0_DDR_DM;

inout [3:0] processing_system7_0_DDR_DQS;

inout [3:0] processing_system7_0_DDR_DQS_n;

inout processing_system7_0_DDR_VRN;

inout processing_system7_0_DDR_VRP;

input [63:0] processing_system7_0_GPIO_I_pin;

output [63:0] processing_system7_0_GPIO_O_pin;

output [63:0] processing_system7_0_GPIO_T_pin;

output processing_system7_0_FCLK_CLK0_pin;

output processing_system7_0_FCLK_CLK1_pin;

output processing_system7_0_FCLK_CLK2_pin;

output processing_system7_0_FCLK_CLK3_pin;

output axi_apb_bridge_0_M_APB_PCLK_pin;

output axi_apb_bridge_0_M_APB_PRESETN_pin;

output [31:0] axi_apb_bridge_0_M_APB_PADDR_pin;

output [3:0] axi_apb_bridge_0_M_APB_PSEL_pin;

output axi_apb_bridge_0_M_APB_PENABLE_pin;

output axi_apb_bridge_0_M_APB_PWRITE_pin;

output [31:0] axi_apb_bridge_0_M_APB_PWDATA_pin;

input [3:0] axi_apb_bridge_0_M_APB_PREADY_pin;

input [31:0] axi_apb_bridge_0_M_APB_PRDATA_pin;

input [31:0] axi_apb_bridge_0_M_APB_PRDATA2_pin;

input [31:0] axi_apb_bridge_0_M_APB_PRDATA3_pin;

input [31:0] axi_apb_bridge_0_M_APB_PRDATA4_pin;

input [3:0] axi_apb_bridge_0_M_APB_PSLVERR_pin;

output processing_system7_0_S_AXI_HP0_ARREADY_pin;

output processing_system7_0_S_AXI_HP0_AWREADY_pin;

output processing_system7_0_S_AXI_HP0_BVALID_pin;

output processing_system7_0_S_AXI_HP0_RLAST_pin;

output processing_system7_0_S_AXI_HP0_RVALID_pin;

output processing_system7_0_S_AXI_HP0_WREADY_pin;

output [1:0] processing_system7_0_S_AXI_HP0_BRESP_pin;

output [1:0] processing_system7_0_S_AXI_HP0_RRESP_pin;

output [5:0] processing_system7_0_S_AXI_HP0_BID_pin;

output [5:0] processing_system7_0_S_AXI_HP0_RID_pin;

output [63:0] processing_system7_0_S_AXI_HP0_RDATA_pin;

input processing_system7_0_S_AXI_HP0_ACLK_pin;

input processing_system7_0_S_AXI_HP0_ARVALID_pin;

input processing_system7_0_S_AXI_HP0_AWVALID_pin;

input processing_system7_0_S_AXI_HP0_BREADY_pin;

input processing_system7_0_S_AXI_HP0_RREADY_pin;

input processing_system7_0_S_AXI_HP0_WLAST_pin;

input processing_system7_0_S_AXI_HP0_WVALID_pin;

input [1:0] processing_system7_0_S_AXI_HP0_ARBURST_pin;

input [1:0] processing_system7_0_S_AXI_HP0_ARLOCK_pin;

input [2:0] processing_system7_0_S_AXI_HP0_ARSIZE_pin;

input [1:0] processing_system7_0_S_AXI_HP0_AWBURST_pin;

input [1:0] processing_system7_0_S_AXI_HP0_AWLOCK_pin;

input [2:0] processing_system7_0_S_AXI_HP0_AWSIZE_pin;

input [2:0] processing_system7_0_S_AXI_HP0_ARPROT_pin;

input [2:0] processing_system7_0_S_AXI_HP0_AWPROT_pin;

input [31:0] processing_system7_0_S_AXI_HP0_ARADDR_pin;

input [31:0] processing_system7_0_S_AXI_HP0_AWADDR_pin;

input [3:0] processing_system7_0_S_AXI_HP0_ARCACHE_pin;

input [3:0] processing_system7_0_S_AXI_HP0_ARLEN_pin;

input [3:0] processing_system7_0_S_AXI_HP0_ARQOS_pin;

input [3:0] processing_system7_0_S_AXI_HP0_AWCACHE_pin;

input [3:0] processing_system7_0_S_AXI_HP0_AWLEN_pin;

input [3:0] processing_system7_0_S_AXI_HP0_AWQOS_pin;

input [5:0] processing_system7_0_S_AXI_HP0_ARID_pin;

input [5:0] processing_system7_0_S_AXI_HP0_AWID_pin;

input [5:0] processing_system7_0_S_AXI_HP0_WID_pin;

input [63:0] processing_system7_0_S_AXI_HP0_WDATA_pin;

input [7:0] processing_system7_0_S_AXI_HP0_WSTRB_pin;

(* BOX_TYPE = "user_black_box" *)

ps_module

ps_module_i (

.processing_system7_0_MIO ( processing_system7_0_MIO ),

.processing_system7_0_PS_SRSTB_pin ( processing_system7_0_PS_SRSTB_pin ),

.processing_system7_0_PS_CLK_pin ( processing_system7_0_PS_CLK_pin ),

.processing_system7_0_PS_PORB_pin ( processing_system7_0_PS_PORB_pin ),

.processing_system7_0_DDR_Clk ( processing_system7_0_DDR_Clk ),

.processing_system7_0_DDR_Clk_n ( processing_system7_0_DDR_Clk_n ),

.processing_system7_0_DDR_CKE ( processing_system7_0_DDR_CKE ),

.processing_system7_0_DDR_CS_n ( processing_system7_0_DDR_CS_n ),

.processing_system7_0_DDR_RAS_n ( processing_system7_0_DDR_RAS_n ),

.processing_system7_0_DDR_CAS_n ( processing_system7_0_DDR_CAS_n ),

.processing_system7_0_DDR_WEB_pin ( processing_system7_0_DDR_WEB_pin ),

.processing_system7_0_DDR_BankAddr ( processing_system7_0_DDR_BankAddr ),

.processing_system7_0_DDR_Addr ( processing_system7_0_DDR_Addr ),

.processing_system7_0_DDR_ODT ( processing_system7_0_DDR_ODT ),

.processing_system7_0_DDR_DRSTB ( processing_system7_0_DDR_DRSTB ),

.processing_system7_0_DDR_DQ ( processing_system7_0_DDR_DQ ),

.processing_system7_0_DDR_DM ( processing_system7_0_DDR_DM ),

.processing_system7_0_DDR_DQS ( processing_system7_0_DDR_DQS ),

.processing_system7_0_DDR_DQS_n ( processing_system7_0_DDR_DQS_n ),

.processing_system7_0_DDR_VRN ( processing_system7_0_DDR_VRN ),

.processing_system7_0_DDR_VRP ( processing_system7_0_DDR_VRP ),

.processing_system7_0_GPIO_I_pin ( processing_system7_0_GPIO_I_pin ),

.processing_system7_0_GPIO_O_pin ( processing_system7_0_GPIO_O_pin ),

.processing_system7_0_GPIO_T_pin ( processing_system7_0_GPIO_T_pin ),

.processing_system7_0_FCLK_CLK0_pin ( processing_system7_0_FCLK_CLK0_pin ),

.processing_system7_0_FCLK_CLK1_pin ( processing_system7_0_FCLK_CLK1_pin ),

.processing_system7_0_FCLK_CLK2_pin ( processing_system7_0_FCLK_CLK2_pin ),

.processing_system7_0_FCLK_CLK3_pin ( processing_system7_0_FCLK_CLK3_pin ),

.axi_apb_bridge_0_M_APB_PCLK_pin ( axi_apb_bridge_0_M_APB_PCLK_pin ),

.axi_apb_bridge_0_M_APB_PRESETN_pin ( axi_apb_bridge_0_M_APB_PRESETN_pin ),

.axi_apb_bridge_0_M_APB_PADDR_pin ( axi_apb_bridge_0_M_APB_PADDR_pin ),

.axi_apb_bridge_0_M_APB_PSEL_pin ( axi_apb_bridge_0_M_APB_PSEL_pin ),

.axi_apb_bridge_0_M_APB_PENABLE_pin ( axi_apb_bridge_0_M_APB_PENABLE_pin ),

.axi_apb_bridge_0_M_APB_PWRITE_pin ( axi_apb_bridge_0_M_APB_PWRITE_pin ),

.axi_apb_bridge_0_M_APB_PWDATA_pin ( axi_apb_bridge_0_M_APB_PWDATA_pin ),

.axi_apb_bridge_0_M_APB_PREADY_pin ( axi_apb_bridge_0_M_APB_PREADY_pin ),

.axi_apb_bridge_0_M_APB_PRDATA_pin ( axi_apb_bridge_0_M_APB_PRDATA_pin ),

.axi_apb_bridge_0_M_APB_PRDATA2_pin ( axi_apb_bridge_0_M_APB_PRDATA2_pin ),

.axi_apb_bridge_0_M_APB_PRDATA3_pin ( axi_apb_bridge_0_M_APB_PRDATA3_pin ),

.axi_apb_bridge_0_M_APB_PRDATA4_pin ( axi_apb_bridge_0_M_APB_PRDATA4_pin ),

.axi_apb_bridge_0_M_APB_PSLVERR_pin ( axi_apb_bridge_0_M_APB_PSLVERR_pin ),

.processing_system7_0_S_AXI_HP0_ARREADY_pin ( processing_system7_0_S_AXI_HP0_ARREADY_pin ),

.processing_system7_0_S_AXI_HP0_AWREADY_pin ( processing_system7_0_S_AXI_HP0_AWREADY_pin ),

.processing_system7_0_S_AXI_HP0_BVALID_pin ( processing_system7_0_S_AXI_HP0_BVALID_pin ),

.processing_system7_0_S_AXI_HP0_RLAST_pin ( processing_system7_0_S_AXI_HP0_RLAST_pin ),

.processing_system7_0_S_AXI_HP0_RVALID_pin ( processing_system7_0_S_AXI_HP0_RVALID_pin ),

.processing_system7_0_S_AXI_HP0_WREADY_pin ( processing_system7_0_S_AXI_HP0_WREADY_pin ),

.processing_system7_0_S_AXI_HP0_BRESP_pin ( processing_system7_0_S_AXI_HP0_BRESP_pin ),

.processing_system7_0_S_AXI_HP0_RRESP_pin ( processing_system7_0_S_AXI_HP0_RRESP_pin ),

.processing_system7_0_S_AXI_HP0_BID_pin ( processing_system7_0_S_AXI_HP0_BID_pin ),

.processing_system7_0_S_AXI_HP0_RID_pin ( processing_system7_0_S_AXI_HP0_RID_pin ),

.processing_system7_0_S_AXI_HP0_RDATA_pin ( processing_system7_0_S_AXI_HP0_RDATA_pin ),

.processing_system7_0_S_AXI_HP0_ACLK_pin ( processing_system7_0_S_AXI_HP0_ACLK_pin ),

.processing_system7_0_S_AXI_HP0_ARVALID_pin ( processing_system7_0_S_AXI_HP0_ARVALID_pin ),

.processing_system7_0_S_AXI_HP0_AWVALID_pin ( processing_system7_0_S_AXI_HP0_AWVALID_pin ),

.processing_system7_0_S_AXI_HP0_BREADY_pin ( processing_system7_0_S_AXI_HP0_BREADY_pin ),

.processing_system7_0_S_AXI_HP0_RREADY_pin ( processing_system7_0_S_AXI_HP0_RREADY_pin ),

.processing_system7_0_S_AXI_HP0_WLAST_pin ( processing_system7_0_S_AXI_HP0_WLAST_pin ),

.processing_system7_0_S_AXI_HP0_WVALID_pin ( processing_system7_0_S_AXI_HP0_WVALID_pin ),

.processing_system7_0_S_AXI_HP0_ARBURST_pin ( processing_system7_0_S_AXI_HP0_ARBURST_pin ),

.processing_system7_0_S_AXI_HP0_ARLOCK_pin ( processing_system7_0_S_AXI_HP0_ARLOCK_pin ),

.processing_system7_0_S_AXI_HP0_ARSIZE_pin ( processing_system7_0_S_AXI_HP0_ARSIZE_pin ),

.processing_system7_0_S_AXI_HP0_AWBURST_pin ( processing_system7_0_S_AXI_HP0_AWBURST_pin ),

.processing_system7_0_S_AXI_HP0_AWLOCK_pin ( processing_system7_0_S_AXI_HP0_AWLOCK_pin ),

.processing_system7_0_S_AXI_HP0_AWSIZE_pin ( processing_system7_0_S_AXI_HP0_AWSIZE_pin ),

.processing_system7_0_S_AXI_HP0_ARPROT_pin ( processing_system7_0_S_AXI_HP0_ARPROT_pin ),

.processing_system7_0_S_AXI_HP0_AWPROT_pin ( processing_system7_0_S_AXI_HP0_AWPROT_pin ),

.processing_system7_0_S_AXI_HP0_ARADDR_pin ( processing_system7_0_S_AXI_HP0_ARADDR_pin ),

.processing_system7_0_S_AXI_HP0_AWADDR_pin ( processing_system7_0_S_AXI_HP0_AWADDR_pin ),

.processing_system7_0_S_AXI_HP0_ARCACHE_pin ( processing_system7_0_S_AXI_HP0_ARCACHE_pin ),

.processing_system7_0_S_AXI_HP0_ARLEN_pin ( processing_system7_0_S_AXI_HP0_ARLEN_pin ),

.processing_system7_0_S_AXI_HP0_ARQOS_pin ( processing_system7_0_S_AXI_HP0_ARQOS_pin ),

.processing_system7_0_S_AXI_HP0_AWCACHE_pin ( processing_system7_0_S_AXI_HP0_AWCACHE_pin ),

.processing_system7_0_S_AXI_HP0_AWLEN_pin ( processing_system7_0_S_AXI_HP0_AWLEN_pin ),

.processing_system7_0_S_AXI_HP0_AWQOS_pin ( processing_system7_0_S_AXI_HP0_AWQOS_pin ),

.processing_system7_0_S_AXI_HP0_ARID_pin ( processing_system7_0_S_AXI_HP0_ARID_pin ),

.processing_system7_0_S_AXI_HP0_AWID_pin ( processing_system7_0_S_AXI_HP0_AWID_pin ),

.processing_system7_0_S_AXI_HP0_WID_pin ( processing_system7_0_S_AXI_HP0_WID_pin ),

.processing_system7_0_S_AXI_HP0_WDATA_pin ( processing_system7_0_S_AXI_HP0_WDATA_pin ),

.processing_system7_0_S_AXI_HP0_WSTRB_pin ( processing_system7_0_S_AXI_HP0_WSTRB_pin )

);

endmodule 一気に信号が増えましたが、「axi_apb_bridge_0_M_APB」がAPB関連、「processing_system7_0_S_AXI_HP0」がAXI_HP関連です。基本一対一でつなぐだけなので、私はエディタのコピペと置換とマクロで半自動的につないでます。ところで、自動的にできるんならツールに任せようよ、ってできたツールがSOPC Builder、Qsys、XPSなどです。XPSの作業は終了。後は普通にロジック作るだけです。