HP ProLiant G7 ML110 ESXi導入 [PC]

さて、とりあえずOI151a入れて低消費電力サーバーとしてひとまず安定してるこのサーバーですが、これだけ素性が良いとやっぱり欲が出てきます。FPGAのコンパイル任せたりとか、あれやこれや・・・そうなるとWindows系とLinux系の環境が欲しくなります。仮想環境?

でもzfsをストレージとして使いたいのでSolaris系は残したい。VirtualBoxも考えましたが、やはりここはハイパーバイザー、VMware ESXiでしょう!。何しろハイパーだし(笑)Solaris系の仮想環境はイマイチよくわかりません。

ということで早速USBを別の2GBのに差し替え、VMwareのからESXi 5.0をダウンロード、同時にライセンスも取得、CDRに焼いて起動。BIOSのパワー制御の設定は「OS Control」にしておかないとピンク画面になるそうです。

インストールに関してはたくさん紹介されてるので割愛。G7でも普通通り導入できました。SSH開放してvSphere Clientインストールしてハイパーバイザー環境があっさりできあがり。上手く行ったらメモリを16GBにしようかな~とか考えてます。

ESXiは仮想マシンのファイルを置いておくデータストレージが必要です。外部のiSCSIやNFSサーバーを使うのが想定された使い方ですが、別途サーバーを置くのは避けたいので、内部のSATAに小容量のSSDを接続。データストレージとします。

仮想環境でも普段通りOI151aのインストールは完了します。物理的なCDRではなくISOファイルが使えるのでさらに楽です。

raidz2ボリュームのimport。ここで分かれ目です。zfsのHDDはESXi側で認識されているので、仮想マシンへそのまま渡すにはRDM(Raw Device Mapping)にしなくてはなりません。RDMのやり方は"ESXi RDM"などで検索するとたくさん出てきます。SSHコンソールから、

ただ、自分の環境ではスピンダウンの設定が上手く働きません。何か設定おかしいのかな?HDDの健康のため回しっぱなしならRDMでも良いのですが…

もう一つの方法、「PCI PassThrough」があります。HDDのコントローラ丸ごと仮想環境に渡してしまうという秘技です。これなら!……標準のCeleron G530はこれが出来ません。Vt-dが無効になってるんです。

PCIパススルーをやってみたい。この辺から目的と手段を入れ違えてます(先のRDMで一応の目的は達成されてるのですから)。ということで「Xeon E3 1220L」を購入。HPがラインアップしてるのは1220(L無し。4コア4スレッド)で、こちらの方が確実に動作するのですが、2コア4スレッド、TPD20Wに惹かれ、ちょっと冒険です。

CPU換装にはT15のトルクスドライバー(星形のやつ)が必要ですが、どのご家庭にも必ず1本はあるので問題ないでしょう。グリスを塗り直してヒートシンクを戻し、電源投入。…3分ぐらい画面真っ黒でした。やってしまったかと思った頃、画面が出て「1220L」の文字が!ちゃんと認識されてるようです。

※本来のターボ動作をしてるかは未確認です。

消費電力はあまり変わらないみたいです。同じ2コアのSandy Bridgeでキャッシュが1.5倍、HTが有効という差です。アイドルで気持ち1~2W高い感じでしょうか。

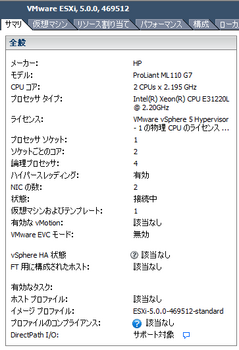

さっそくvShpere Clientからの確認。

サマリ

サマリ

ばっちり。

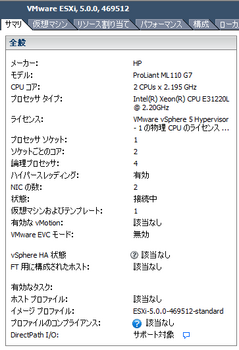

パススルーの設定画面。

パススルー

パススルー

完璧っ!……え?6ポート?

ヤな予感を感じつつ、リブートしたところ…やはり、ストレージとして使ってたSATA接続のSSDもまとめてパススルーされ、ESXiから見えなくなってましたよorz

当たり前といえば当たり前。が、気づきませんでした。

どこかからESXiのデータストレージを確保しなくてはなりませんが、ESXiはUSBのストレージを許してません※。PCIeに拡張しようにもSilcon Imageなどの安いカードは軒並み全滅。Adaptecなど有名どころなら使えますが、価格と消費電力、そしてG7のファンの騒音が増える(別のカードで確認済み)ので躊躇してます。G7単体では手詰まりです。

外部に別途NFSサーバーを立てて、そこにストレージを作り、OI151aをインストール、パススルーさせたHDDのコントローラのzfsのアクセス。これは上手くいってます。が、サーバーを別に用意するのは…これはさっきも書きましたね。

RDMかRAIDカードかNFSサーバーか、の3択となりました。

今はOI151aに戻してます。VirtualBoxを入れてみようかと。

ちょっと前ならI/OデータのUSL-5Pとかで試したいところですが、さすがに入手が…NFSが出来るのかも情報少ないですし。OpenBlockSなどなら安全そうですが、ちょっと高いな…

ということで密かに「Raspberry Pi」に期待してます。NFSサーバーが動くかは知らないのですが、SDカードをNFS exportできれば1W以下のデータストレージとして使えないかな、と。

※追記

色々試してはいますが自分のスキルでは無理そう

・usbarbitratorを止める。

→これを止めると仮想マシンに渡されてたUSBメモリがESXiに戻ってくる。

・/dev/disksにUSBデバイス出てくる。

・fdiskでパーティション作成、タイプをvmfsにする。

・vmkfstoolでvmfs作成。

→失敗。カーネルがサポートしてないよ~的なエラーが出る。

modprobeとかで見るとvmfsはあるが、usbをファイルシステムとして扱うモジュールが無さそう?

で、あきらめ状態。

でもzfsをストレージとして使いたいのでSolaris系は残したい。VirtualBoxも考えましたが、やはりここはハイパーバイザー、VMware ESXiでしょう!。何しろハイパーだし(笑)Solaris系の仮想環境はイマイチよくわかりません。

ということで早速USBを別の2GBのに差し替え、VMwareのからESXi 5.0をダウンロード、同時にライセンスも取得、CDRに焼いて起動。BIOSのパワー制御の設定は「OS Control」にしておかないとピンク画面になるそうです。

インストールに関してはたくさん紹介されてるので割愛。G7でも普通通り導入できました。SSH開放してvSphere Clientインストールしてハイパーバイザー環境があっさりできあがり。上手く行ったらメモリを16GBにしようかな~とか考えてます。

ESXiは仮想マシンのファイルを置いておくデータストレージが必要です。外部のiSCSIやNFSサーバーを使うのが想定された使い方ですが、別途サーバーを置くのは避けたいので、内部のSATAに小容量のSSDを接続。データストレージとします。

仮想環境でも普段通りOI151aのインストールは完了します。物理的なCDRではなくISOファイルが使えるのでさらに楽です。

raidz2ボリュームのimport。ここで分かれ目です。zfsのHDDはESXi側で認識されているので、仮想マシンへそのまま渡すにはRDM(Raw Device Mapping)にしなくてはなりません。RDMのやり方は"ESXi RDM"などで検索するとたくさん出てきます。SSHコンソールから、

# vmkfstools -z /vmfs/devices/disks/"妙に長いHDDの名前" ./"RDMファイルの名前".vmdk -a lsilogicと台数分RDMのファイルを作成し、仮想マシンに追加すればOKとなります。raidz2の4台のHDDも問題なく登録され、仮想oiから"zpool import"でマウントできます。データ転送速度もネイティブ並み、scrubも通ってます。

ただ、自分の環境ではスピンダウンの設定が上手く働きません。何か設定おかしいのかな?HDDの健康のため回しっぱなしならRDMでも良いのですが…

もう一つの方法、「PCI PassThrough」があります。HDDのコントローラ丸ごと仮想環境に渡してしまうという秘技です。これなら!……標準のCeleron G530はこれが出来ません。Vt-dが無効になってるんです。

PCIパススルーをやってみたい。この辺から目的と手段を入れ違えてます(先のRDMで一応の目的は達成されてるのですから)。ということで「Xeon E3 1220L」を購入。HPがラインアップしてるのは1220(L無し。4コア4スレッド)で、こちらの方が確実に動作するのですが、2コア4スレッド、TPD20Wに惹かれ、ちょっと冒険です。

CPU換装にはT15のトルクスドライバー(星形のやつ)が必要ですが、どのご家庭にも必ず1本はあるので問題ないでしょう。グリスを塗り直してヒートシンクを戻し、電源投入。…3分ぐらい画面真っ黒でした。やってしまったかと思った頃、画面が出て「1220L」の文字が!ちゃんと認識されてるようです。

※本来のターボ動作をしてるかは未確認です。

消費電力はあまり変わらないみたいです。同じ2コアのSandy Bridgeでキャッシュが1.5倍、HTが有効という差です。アイドルで気持ち1~2W高い感じでしょうか。

さっそくvShpere Clientからの確認。

サマリ

サマリばっちり。

パススルーの設定画面。

パススルー

パススルー完璧っ!……え?6ポート?

ヤな予感を感じつつ、リブートしたところ…やはり、ストレージとして使ってたSATA接続のSSDもまとめてパススルーされ、ESXiから見えなくなってましたよorz

当たり前といえば当たり前。が、気づきませんでした。

どこかからESXiのデータストレージを確保しなくてはなりませんが、ESXiはUSBのストレージを許してません※。PCIeに拡張しようにもSilcon Imageなどの安いカードは軒並み全滅。Adaptecなど有名どころなら使えますが、価格と消費電力、そしてG7のファンの騒音が増える(別のカードで確認済み)ので躊躇してます。G7単体では手詰まりです。

外部に別途NFSサーバーを立てて、そこにストレージを作り、OI151aをインストール、パススルーさせたHDDのコントローラのzfsのアクセス。これは上手くいってます。が、サーバーを別に用意するのは…これはさっきも書きましたね。

RDMかRAIDカードかNFSサーバーか、の3択となりました。

今はOI151aに戻してます。VirtualBoxを入れてみようかと。

ちょっと前ならI/OデータのUSL-5Pとかで試したいところですが、さすがに入手が…NFSが出来るのかも情報少ないですし。OpenBlockSなどなら安全そうですが、ちょっと高いな…

ということで密かに「Raspberry Pi」に期待してます。NFSサーバーが動くかは知らないのですが、SDカードをNFS exportできれば1W以下のデータストレージとして使えないかな、と。

※追記

色々試してはいますが自分のスキルでは無理そう

・usbarbitratorを止める。

→これを止めると仮想マシンに渡されてたUSBメモリがESXiに戻ってくる。

・/dev/disksにUSBデバイス出てくる。

・fdiskでパーティション作成、タイプをvmfsにする。

・vmkfstoolでvmfs作成。

→失敗。カーネルがサポートしてないよ~的なエラーが出る。

modprobeとかで見るとvmfsはあるが、usbをファイルシステムとして扱うモジュールが無さそう?

で、あきらめ状態。

AXIの勉強(その1) [AXI]

そのいくつまで行くかは不明ですが。

参考にしているのはARM本家の仕様書やXilinxの資料など。まだベータですがAlteraのQsysも追いかけてます。

タイミングチャートの作成にはTimingChartViewerをお借りしてます。同期回路限定ですが便利に使わせていただいてます。ありがとうございます。

用語とか勝手に呼び替えてしまってるところがあります。適当に読み替えて下さい。

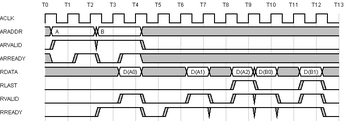

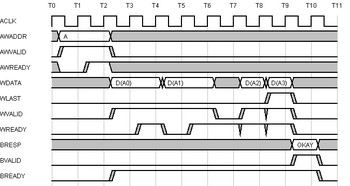

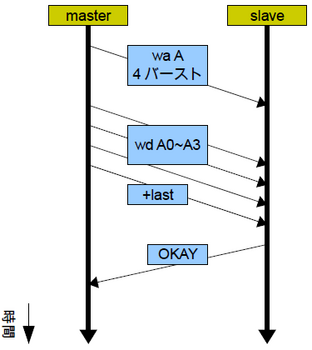

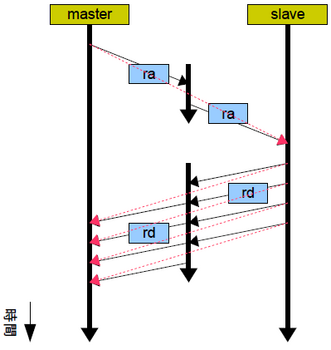

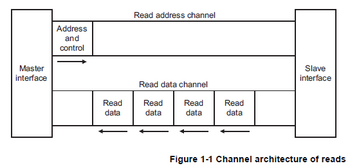

AXIのタイミングは、良く資料などでも出てきますが、

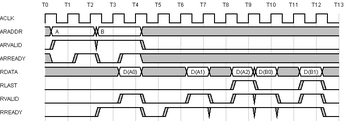

リード

リード

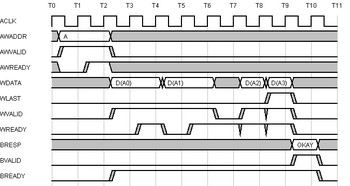

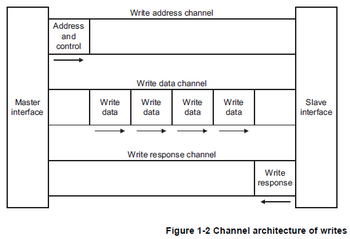

ライト

ライト

という感じです。

なんか複雑そうですが、実はタイミングとして見ないとならないのは"ready"と"valid"だけです。もう一つのAXI規格の「AXI stream」もそうですが、"ready"と"valid"が両方とも"1"(有効)の時にデータ(荷物、ペイロード)が転送される、という仕組みになってます。この仕組みはAXI3もAXI4も同じです。

図中の"last"信号や、"id"、"size"、"burst"、"lock"などいろいろな信号がありますが、これら全て荷物、ペイロードとして扱います。"ready"と"valid"と"荷物"という関係です。

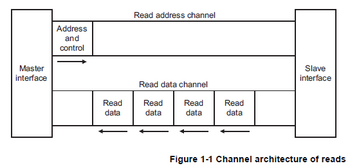

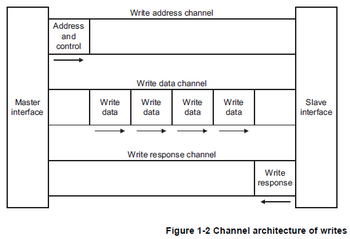

これに関してはARMの資料にも記述されてます。以下抜粋ですが、これもよく見かける図ですね。

リード

リード

ライト

ライト

この図だと、リードが2チャンネルで、ライトが3チャンネルとアンバランスな感じがしますが、リードのデータチャンネルにライトのレスポンスと同等の情報が載ってるので(OKAYなどを返してる)、行き交う情報の量はだいたい対称です。

届いた荷物の中身が重要であって、荷物がいつ届いたかに関してはあまり考えなくて良くなります。マスター側は荷物の準備が出来たら"valid"を有効にする、スレーブ側は荷物の受け入れ準備が出来たら"ready"を有効にする、両方が有効なら転送成立、という考え方です。

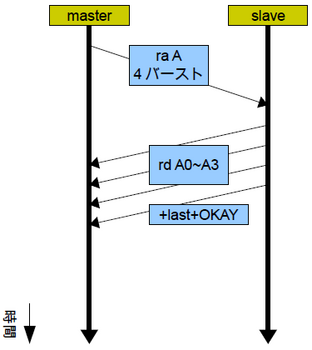

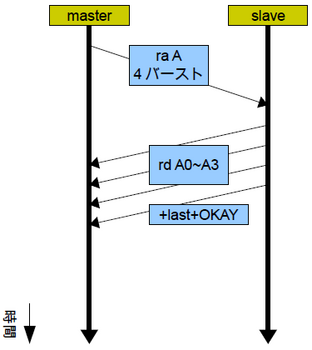

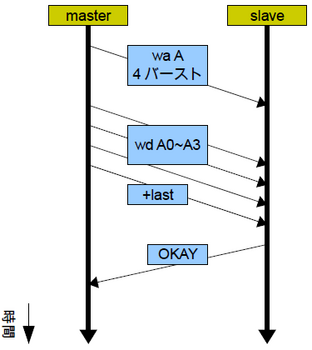

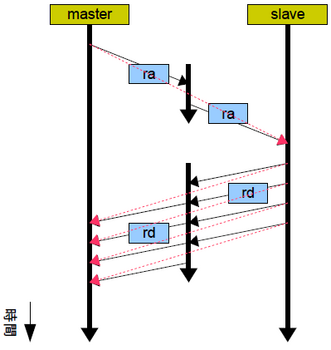

ちょっと図を変えるとその分野の人には見慣れた図になったりします。

リード

リード

ライト

ライト

ra、waはリードライトのアドレス、rd、wdはデータ、+lastはフラグを付加といった感じです。RS-232Cやネットワークとかの通信でもよく見る、データ通信プロトコルの図になりました。

AXIって物理的な通信経路が複数本あるだけで考え方はネットワークに近いと見た方が良いと私は思ってます。ユーザーが作るマスター・スレーブの回路は、このプロトコルを処理するシーケンサーという事になります。

これによる最大の利点、設計時にタイミングのことを考えなくて良い(タイミングとプロトコルを分けて考えられる)という点だと思います。例えばマスターとスレーブが離れた位置にあって、信号到達までに時間がかかり速度が出ない、という場合、通信経路にレジスタを入れて経路を分割してもプロトコル上は影響ありません。

リード、経路分割

リード、経路分割

途中にレジスタが入って経路が分割されても通信は成り立ちます。見た目には赤点線のように、到着時間が変わった=矢印の傾きが変わった、のと等価です。

レジスタが入ってるので、個々のチャンネルのタイミングは大きく変わってるはずです。が、AXIは届いた荷物の中身が重要で、届きさえすれば良いという仕組みですから、タイミングの違いは無視してかまわない事になります。これが設計をすごく楽にします。

個々のチャンネルはAXIのストリームと同じですから、次からはその辺の部品を作っていきたいと思います。

参考にしているのはARM本家の仕様書やXilinxの資料など。まだベータですがAlteraのQsysも追いかけてます。

タイミングチャートの作成にはTimingChartViewerをお借りしてます。同期回路限定ですが便利に使わせていただいてます。ありがとうございます。

用語とか勝手に呼び替えてしまってるところがあります。適当に読み替えて下さい。

AXIのタイミングは、良く資料などでも出てきますが、

リード

リード ライト

ライトという感じです。

なんか複雑そうですが、実はタイミングとして見ないとならないのは"ready"と"valid"だけです。もう一つのAXI規格の「AXI stream」もそうですが、"ready"と"valid"が両方とも"1"(有効)の時にデータ(荷物、ペイロード)が転送される、という仕組みになってます。この仕組みはAXI3もAXI4も同じです。

図中の"last"信号や、"id"、"size"、"burst"、"lock"などいろいろな信号がありますが、これら全て荷物、ペイロードとして扱います。"ready"と"valid"と"荷物"という関係です。

これに関してはARMの資料にも記述されてます。以下抜粋ですが、これもよく見かける図ですね。

リード

リード ライト

ライトこの図だと、リードが2チャンネルで、ライトが3チャンネルとアンバランスな感じがしますが、リードのデータチャンネルにライトのレスポンスと同等の情報が載ってるので(OKAYなどを返してる)、行き交う情報の量はだいたい対称です。

届いた荷物の中身が重要であって、荷物がいつ届いたかに関してはあまり考えなくて良くなります。マスター側は荷物の準備が出来たら"valid"を有効にする、スレーブ側は荷物の受け入れ準備が出来たら"ready"を有効にする、両方が有効なら転送成立、という考え方です。

ちょっと図を変えるとその分野の人には見慣れた図になったりします。

リード

リード ライト

ライトra、waはリードライトのアドレス、rd、wdはデータ、+lastはフラグを付加といった感じです。RS-232Cやネットワークとかの通信でもよく見る、データ通信プロトコルの図になりました。

AXIって物理的な通信経路が複数本あるだけで考え方はネットワークに近いと見た方が良いと私は思ってます。ユーザーが作るマスター・スレーブの回路は、このプロトコルを処理するシーケンサーという事になります。

これによる最大の利点、設計時にタイミングのことを考えなくて良い(タイミングとプロトコルを分けて考えられる)という点だと思います。例えばマスターとスレーブが離れた位置にあって、信号到達までに時間がかかり速度が出ない、という場合、通信経路にレジスタを入れて経路を分割してもプロトコル上は影響ありません。

リード、経路分割

リード、経路分割途中にレジスタが入って経路が分割されても通信は成り立ちます。見た目には赤点線のように、到着時間が変わった=矢印の傾きが変わった、のと等価です。

レジスタが入ってるので、個々のチャンネルのタイミングは大きく変わってるはずです。が、AXIは届いた荷物の中身が重要で、届きさえすれば良いという仕組みですから、タイミングの違いは無視してかまわない事になります。これが設計をすごく楽にします。

個々のチャンネルはAXIのストリームと同じですから、次からはその辺の部品を作っていきたいと思います。

念のため

ここに置いてあるコンテンツ(HDLなど)は非商用目的に限りご利用いただけます。

実務で使う方がいるとは思いませんが、念のため。

実務で使う方がいるとは思いませんが、念のため。

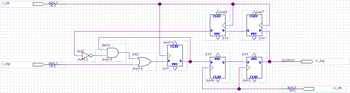

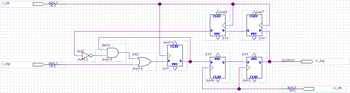

部品(クロック載せ替え) [HDL]

信号のクロック載せ替えを行うモジュールです。

こういうモジュールでは非同期リセットを使ってます。

i_clkに同期したi_sigを、o_clkに同期したo_sigにつなぎます。sigwパラメーターは信号の本数です。i→oへ載せ替えた信号(fwd)を、o→iへ載せ替え返して戻します(ret)。相手が信号を受け取ったことを確認するためです。ハンドシェイクを行っているので、双方のクロックの周波数がどんな関係でも使えます。

fwd、retの[1]は必ずメタステーブル状態になるので使えません。[2]以降も可能性はありますが確率は下がるのでこれを使います。できれば[1]~[2]以降の距離(遅延時間)に制約をかけます。

modeでそのまま、立ち上がり、立ち下がりを切り替えてます。

複数本数の信号が載せ替えられますが、当然データのやりとりには使えません。それぞれ独立した信号として扱います。

回路図追加。リセットとかエッジの記述は省いてます。仕組みはわかりやすいですが、AND-ORの部分はHDLの方がわかりやすそうです。

こういうモジュールでは非同期リセットを使ってます。

i_clkに同期したi_sigを、o_clkに同期したo_sigにつなぎます。sigwパラメーターは信号の本数です。i→oへ載せ替えた信号(fwd)を、o→iへ載せ替え返して戻します(ret)。相手が信号を受け取ったことを確認するためです。ハンドシェイクを行っているので、双方のクロックの周波数がどんな関係でも使えます。

fwd、retの[1]は必ずメタステーブル状態になるので使えません。[2]以降も可能性はありますが確率は下がるのでこれを使います。できれば[1]~[2]以降の距離(遅延時間)に制約をかけます。

modeでそのまま、立ち上がり、立ち下がりを切り替えてます。

`timescale 1ns / 1ps

`default_nettype none

module signal_transit

#(

parameter sigw = 1, // signal width

parameter mode = "" // mode, "","UP","DOWN"

)

(

// common

input wire a_rst, // Async Reset

// input

input wire i_clk, // clock

input wire [sigw-1:0] i_sig, // signal

// output

input wire o_clk, // clock

output reg [sigw-1:0] o_sig // signal

);

generate

genvar i;

for (i = 0; i < sigw; i = i+1) begin : sigwL

reg [3:1] fwd; // [1] may have meta-state

reg [2:1] ret; // [1] may have meta-state

reg i_trg;

always @(posedge a_rst or posedge i_clk) begin

if (a_rst) begin

i_trg <= 'b0;

ret <= 'b0;

end

else begin

if (i_sig[i] ) i_trg <= 1'b1;

else if (ret[2]) i_trg <= 1'b0;

ret <= {ret[ 1], fwd[2]}; // return

end

end

always @(posedge a_rst or posedge o_clk) begin

if (a_rst) begin

fwd <= 'b0;

o_sig[i] <= 'b0;

end

else begin

fwd <= {fwd[2:1], i_trg }; // forward

if (mode == "UP") o_sig[i] <= (fwd[3:2] == 2'b01); // Up-Edge

else if (mode == "DOWN") o_sig[i] <= (fwd[3:2] == 2'b10); // Down-Edge

else o_sig[i] <= fwd[2]; // Normal

end

end

end

endgenerate

endmodule

`default_nettype wire

複数本数の信号が載せ替えられますが、当然データのやりとりには使えません。それぞれ独立した信号として扱います。

回路図追加。リセットとかエッジの記述は省いてます。仕組みはわかりやすいですが、AND-ORの部分はHDLの方がわかりやすそうです。