Vivado HLS を使ってみた(その6) [FPGA]

リアルタイムでFullHD 1080p60ぐらいは処理して欲しいですよね。

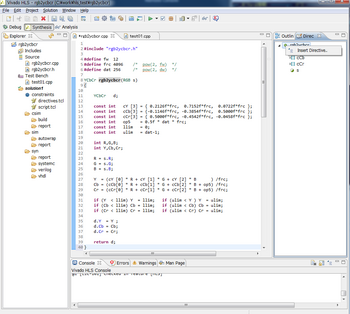

ソースは(その5)のintバージョン。

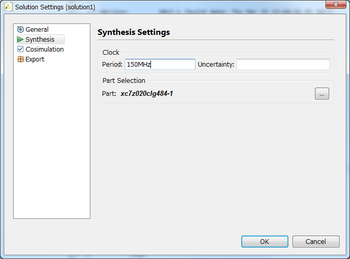

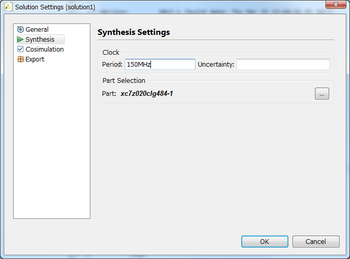

1080pで148.5MHzなので、ソリューションの周波数を150MHzにしてみます。

MHzを付けると周波数と認識されるようです。

これで合成すると…(レポートファイル)

1クロックに1つ答えが得られない困るので、ディレクティブ(指示子)を与えます。おぉ、やっと機種依存するところが出てきた(笑)

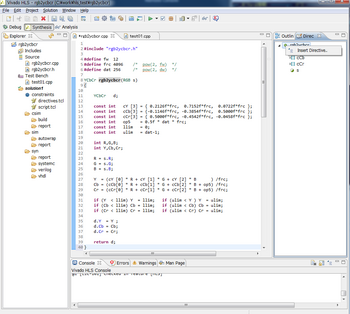

「Directive」タブを開き、関数(rgb2ycbcr)を右クリックします。

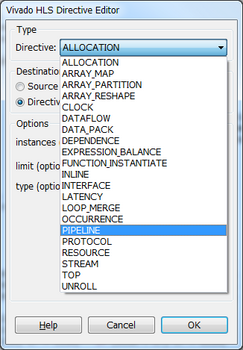

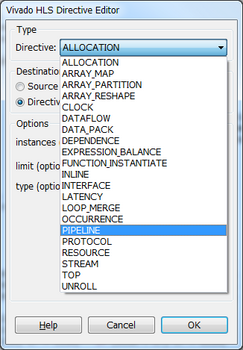

ディレクティブの選択画面が出るので「PIPELINE」を選択します。「Source File」を選ぶと「#pragma HLS PIPELINE」がcppソースに埋め込まれます。「Directive File」を選ぶとディレクティブの別のファイルに保存されます。どちらでも効能は同じ。好みの方にします。

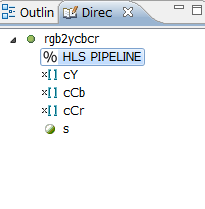

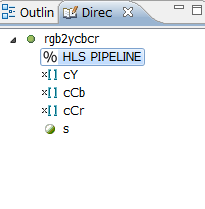

「Directive File」を選んだ場合。ディレクティブのタブに新しく「HLS_PIPELINE」が追加されます。

これで合成開始。

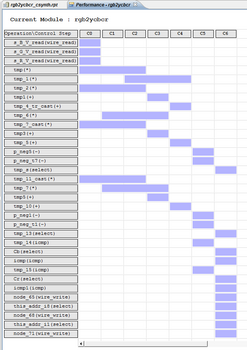

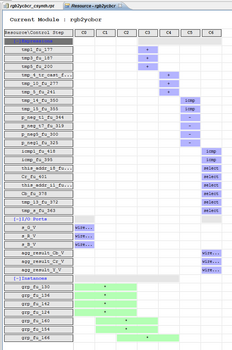

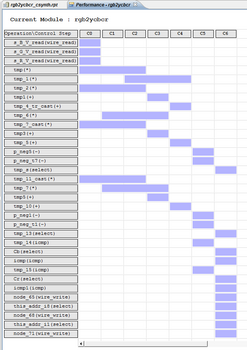

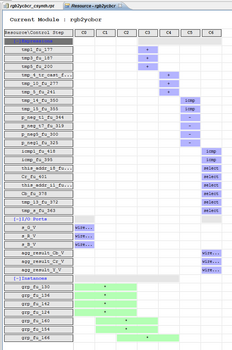

データの流れとリソース。

パイプライン化され、1クロックで1個結果が出てくるようになりました。予想周波数は5.47[ns](約182MHz)。

この辺でいい加減一度ぐらいHDLシミュレーションしておかないと…いままでCのシミュレーションが楽で楽で…改めて思う…HDLのテストベンチってめんどくさい…

中身はほぼ同じで、BMPファイルを流し込んで結果を保存します。ただ、色々書くのが面倒なので、BGRをCbYCrに置き換えたBMPファイルだけ作成します。

ちなみにI/Oピンの情報はレポートファイルの一番下に書かれています。細かい制御方法はXilinxの資料にゆずりますが、今回はI/Oになにも指定していないので、関数の返値(YCbCr)に「ap_ctrl_hs」が、引数(RGB)に「ap_none」が設定されています。Y,Cb,Crそれぞれに「_ap_vld」という信号が付いてますが、この場合「ap_done」と同じ信号になるので見ません。

・「ap_rst」を解除する。

・「ap_start」を'1'にすると動作開始。

・クロック立ち上がり&「ap_ready」が'1'にだったら次のRGBデータをBMPファイルから与える。

・クロック立ち上がり&「ap_done」が'1'だったらYCbCrデータをBMPファイルに書き込む。

という制御だけになります。

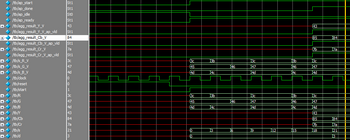

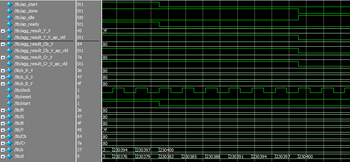

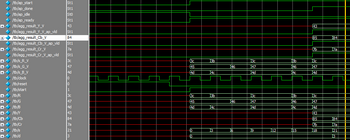

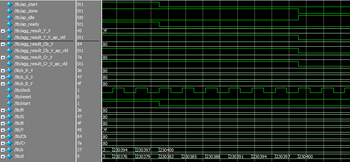

シミュレーションの最初と最後だけ出してみます。

カラーコードにしたので、シミュレーションの最後の値が動いていませんが、これで正常です。下の方のsとdがそれぞれのピクセルカウンタです。

HDLシミュレーションで生成されたBMPファイルと、Cの整数シミュレーションで生成されたBMPファイルのバイナリ比較は完全一致でした。Cの浮動小数点モデルで生成したBMPファイルとの比較では所々1bitの差が出ます。

PlanAheadでインプリしてみます。

ソースは(その5)のintバージョン。

1080pで148.5MHzなので、ソリューションの周波数を150MHzにしてみます。

MHzを付けると周波数と認識されるようです。

これで合成すると…(レポートファイル)

================================================================

== Vivado HLS Report for 'rgb2ycbcr'

================================================================

* Date:

* Version: 2013.1

* Project: rgb2ycbcr

* Solution: solution1

* Product family: zynq zynq_fpv6

* Target device: xc7z020clg484-1

================================================================

== Performance Estimates

================================================================

+ Timing (ns):

* Summary:

+---------+-------+----------+------------+

| Clock | Target| Estimated| Uncertainty|

+---------+-------+----------+------------+

|default | 6.67| 5.47| 0.83|

+---------+-------+----------+------------+

+ Latency (clock cycles):

* Summary:

+-----+-----+-----+-----+---------+

| Latency | Interval | Pipeline|

| min | max | min | max | Type |

+-----+-----+-----+-----+---------+

| 6| 6| 7| 7| none |

+-----+-----+-----+-----+---------+

+ Detail:

* Instance:

N/A

* Loop:

N/A

================================================================

== Utilization Estimates

================================================================

* Summary:

+-----------------+---------+-------+--------+-------+

| Name | BRAM_18K| DSP48E| FF | LUT |

+-----------------+---------+-------+--------+-------+

|Expression | -| -| 0| 235|

|FIFO | -| -| -| -|

|Instance | -| 7| 72| 20|

|Memory | -| -| -| -|

|Multiplexer | -| -| -| -|

|Register | -| -| 231| -|

|ShiftMemory | -| -| -| -|

+-----------------+---------+-------+--------+-------+

|Total | 0| 7| 303| 255|

+-----------------+---------+-------+--------+-------+

|Available | 280| 220| 106400| 53200|

+-----------------+---------+-------+--------+-------+

|Utilization (%) | 0| 3| ~0 | ~0 |

+-----------------+---------+-------+--------+-------+

+ Detail:

* Instance:

+--------------------------------+-----------------------------+---------+-------+----+----+

| Instance | Module | BRAM_18K| DSP48E| FF | LUT|

+--------------------------------+-----------------------------+---------+-------+----+----+

|rgb2ycbcr_mul_8ns_10ns_18_3_U1 |rgb2ycbcr_mul_8ns_10ns_18_3 | 0| 1| 18| 5|

|rgb2ycbcr_mul_8ns_10s_19_3_U5 |rgb2ycbcr_mul_8ns_10s_19_3 | 0| 1| 0| 0|

|rgb2ycbcr_mul_8ns_12ns_20_3_U7 |rgb2ycbcr_mul_8ns_12ns_20_3 | 0| 1| 0| 0|

|rgb2ycbcr_mul_8ns_12s_20_3_U3 |rgb2ycbcr_mul_8ns_12s_20_3 | 0| 1| 18| 5|

|rgb2ycbcr_mul_8ns_12s_20_3_U4 |rgb2ycbcr_mul_8ns_12s_20_3 | 0| 1| 18| 5|

|rgb2ycbcr_mul_8ns_9ns_17_3_U2 |rgb2ycbcr_mul_8ns_9ns_17_3 | 0| 1| 18| 5|

|rgb2ycbcr_mul_8ns_9s_18_3_U6 |rgb2ycbcr_mul_8ns_9s_18_3 | 0| 1| 0| 0|

+--------------------------------+-----------------------------+---------+-------+----+----+

|Total | | 0| 7| 72| 20|

+--------------------------------+-----------------------------+---------+-------+----+----+

* Memory:

N/A

* FIFO:

N/A

* Shift register:

N/A

* Expression:

+--------------------+----------+-------+---+----+------------+------------+

| Variable Name | Operation| DSP48E| FF| LUT| Bitwidth P0| Bitwidth P1|

+--------------------+----------+-------+---+----+------------+------------+

|tmp1_fu_171_p2 | + | 0| 0| 19| 19| 19|

|tmp_10_fu_272_p2 | + | 0| 0| 21| 21| 21|

|tmp_5_fu_236_p2 | + | 0| 0| 21| 21| 21|

|p_neg1_fu_320_p2 | - | 0| 0| 21| 1| 21|

|p_neg5_fu_295_p2 | - | 0| 0| 21| 1| 21|

|p_neg_t1_fu_339_p2 | - | 0| 0| 10| 1| 10|

|p_neg_t7_fu_314_p2 | - | 0| 0| 10| 1| 10|

|Cb_fu_373_p3 | Select | 0| 0| 10| 1| 1|

|Cr_fu_396_p3 | Select | 0| 0| 10| 1| 1|

|agg_result_Cb_V | Select | 0| 0| 8| 1| 2|

|agg_result_Cr_V | Select | 0| 0| 8| 1| 2|

|tmp_13_fu_367_p3 | Select | 0| 0| 10| 1| 10|

|tmp_s_fu_358_p3 | Select | 0| 0| 10| 1| 10|

|icmp1_fu_413_p2 | icmp | 0| 0| 2| 2| 1|

|icmp_fu_390_p2 | icmp | 0| 0| 2| 2| 1|

|tmp_14_fu_345_p2 | icmp | 0| 0| 26| 21| 13|

|tmp_15_fu_350_p2 | icmp | 0| 0| 26| 21| 13|

+--------------------+----------+-------+---+----+------------+------------+

|Total | | 0| 0| 235| 117| 177|

+--------------------+----------+-------+---+----+------------+------------+

* Multiplexer:

N/A

* Register:

+---------------------+----+-----+-----------+

| Name | FF | Bits| Const Bits|

+---------------------+----+-----+-----------+

|G_cast_reg_462 | 8| 20| 12|

|ap_CS_fsm | 3| 3| 0|

|p_neg_t1_reg_556 | 10| 10| 0|

|p_neg_t7_reg_551 | 10| 10| 0|

|tmp1_reg_504 | 19| 19| 0|

|tmp3_cast_reg_509 | 21| 21| 0|

|tmp5_cast_reg_514 | 21| 21| 0|

|tmp_10_reg_535 | 21| 21| 0|

|tmp_11_cast_reg_499 | 20| 20| 0|

|tmp_11_reg_530 | 9| 9| 0|

|tmp_12_reg_541 | 1| 1| 0|

|tmp_14_reg_561 | 1| 1| 0|

|tmp_15_reg_566 | 1| 1| 0|

|tmp_17_reg_546 | 9| 9| 0|

|tmp_2_reg_489 | 17| 17| 0|

|tmp_4_reg_525 | 1| 1| 0|

|tmp_5_reg_519 | 21| 21| 0|

|tmp_7_cast_reg_494 | 20| 20| 0|

|tmp_reg_484 | 18| 18| 0|

+---------------------+----+-----+-----------+

|Total | 231| 243| 12|

+---------------------+----+-----+-----------+

================================================================

== Interface

================================================================

* Summary:

+------------------------+-----+-----+------------+-----------------+--------------+

| RTL Ports | Dir | Bits| Protocol | Source Object | C Type |

+------------------------+-----+-----+------------+-----------------+--------------+

|ap_clk | in | 1| ap_ctrl_hs | rgb2ycbcr | return value |

|ap_rst | in | 1| ap_ctrl_hs | rgb2ycbcr | return value |

|ap_start | in | 1| ap_ctrl_hs | rgb2ycbcr | return value |

|ap_done | out | 1| ap_ctrl_hs | rgb2ycbcr | return value |

|ap_idle | out | 1| ap_ctrl_hs | rgb2ycbcr | return value |

|ap_ready | out | 1| ap_ctrl_hs | rgb2ycbcr | return value |

|agg_result_Y_V | out | 8| ap_vld | agg_result_Y_V | pointer |

|agg_result_Y_V_ap_vld | out | 1| ap_vld | agg_result_Y_V | pointer |

|agg_result_Cb_V | out | 8| ap_vld | agg_result_Cb_V | pointer |

|agg_result_Cb_V_ap_vld | out | 1| ap_vld | agg_result_Cb_V | pointer |

|agg_result_Cr_V | out | 8| ap_vld | agg_result_Cr_V | pointer |

|agg_result_Cr_V_ap_vld | out | 1| ap_vld | agg_result_Cr_V | pointer |

|s_R_V | in | 8| ap_none | s_R_V | scalar |

|s_G_V | in | 8| ap_none | s_G_V | scalar |

|s_B_V | in | 8| ap_none | s_B_V | scalar |

+------------------------+-----+-----+------------+-----------------+--------------+

7クロックに1演算という回路になりました。今回はap_start,ap_doneなどが制御信号として働きます。ap_startで演算開始、ap_doneで計算結果が得られる、という制御になります。1クロックに1つ答えが得られない困るので、ディレクティブ(指示子)を与えます。おぉ、やっと機種依存するところが出てきた(笑)

「Directive」タブを開き、関数(rgb2ycbcr)を右クリックします。

ディレクティブの選択画面が出るので「PIPELINE」を選択します。「Source File」を選ぶと「#pragma HLS PIPELINE」がcppソースに埋め込まれます。「Directive File」を選ぶとディレクティブの別のファイルに保存されます。どちらでも効能は同じ。好みの方にします。

「Directive File」を選んだ場合。ディレクティブのタブに新しく「HLS_PIPELINE」が追加されます。

これで合成開始。

================================================================

== Vivado HLS Report for 'rgb2ycbcr'

================================================================

* Date:

* Version: 2013.1

* Project: rgb2ycbcr

* Solution: solution1

* Product family: zynq zynq_fpv6

* Target device: xc7z020clg484-1

================================================================

== Performance Estimates

================================================================

+ Timing (ns):

* Summary:

+---------+-------+----------+------------+

| Clock | Target| Estimated| Uncertainty|

+---------+-------+----------+------------+

|default | 6.67| 5.47| 0.83|

+---------+-------+----------+------------+

+ Latency (clock cycles):

* Summary:

+-----+-----+-----+-----+----------+

| Latency | Interval | Pipeline |

| min | max | min | max | Type |

+-----+-----+-----+-----+----------+

| 6| 6| 1| 1| function |

+-----+-----+-----+-----+----------+

+ Detail:

* Instance:

N/A

* Loop:

N/A

================================================================

== Utilization Estimates

================================================================

* Summary:

+-----------------+---------+-------+--------+-------+

| Name | BRAM_18K| DSP48E| FF | LUT |

+-----------------+---------+-------+--------+-------+

|Expression | -| -| 0| 235|

|FIFO | -| -| -| -|

|Instance | -| 7| 72| 20|

|Memory | -| -| -| -|

|Multiplexer | -| -| -| -|

|Register | -| -| 287| -|

|ShiftMemory | -| -| 0| 24|

+-----------------+---------+-------+--------+-------+

|Total | 0| 7| 359| 279|

+-----------------+---------+-------+--------+-------+

|Available | 280| 220| 106400| 53200|

+-----------------+---------+-------+--------+-------+

|Utilization (%) | 0| 3| ~0 | ~0 |

+-----------------+---------+-------+--------+-------+

+ Detail:

* Instance:

+--------------------------------+-----------------------------+---------+-------+----+----+

| Instance | Module | BRAM_18K| DSP48E| FF | LUT|

+--------------------------------+-----------------------------+---------+-------+----+----+

|rgb2ycbcr_mul_8ns_10ns_18_3_U1 |rgb2ycbcr_mul_8ns_10ns_18_3 | 0| 1| 18| 5|

|rgb2ycbcr_mul_8ns_10s_19_3_U5 |rgb2ycbcr_mul_8ns_10s_19_3 | 0| 1| 0| 0|

|rgb2ycbcr_mul_8ns_12ns_20_3_U7 |rgb2ycbcr_mul_8ns_12ns_20_3 | 0| 1| 0| 0|

|rgb2ycbcr_mul_8ns_12s_20_3_U3 |rgb2ycbcr_mul_8ns_12s_20_3 | 0| 1| 18| 5|

|rgb2ycbcr_mul_8ns_12s_20_3_U4 |rgb2ycbcr_mul_8ns_12s_20_3 | 0| 1| 18| 5|

|rgb2ycbcr_mul_8ns_9ns_17_3_U2 |rgb2ycbcr_mul_8ns_9ns_17_3 | 0| 1| 18| 5|

|rgb2ycbcr_mul_8ns_9s_18_3_U6 |rgb2ycbcr_mul_8ns_9s_18_3 | 0| 1| 0| 0|

+--------------------------------+-----------------------------+---------+-------+----+----+

|Total | | 0| 7| 72| 20|

+--------------------------------+-----------------------------+---------+-------+----+----+

* Memory:

N/A

* FIFO:

N/A

* Shift register:

+--------------------+---+----+-----+-----------+

| Name | FF| LUT| Bits| Const Bits|

+--------------------+---+----+-----+-----------+

|G_cast_reg_467 | 0| 8| 20| 12|

|s_B_V_read_reg_450 | 0| 8| 8| 0|

|s_R_V_read_reg_456 | 0| 8| 8| 0|

+--------------------+---+----+-----+-----------+

|Total | 0| 24| 36| 12|

+--------------------+---+----+-----+-----------+

* Expression:

+--------------------+----------+-------+---+----+------------+------------+

| Variable Name | Operation| DSP48E| FF| LUT| Bitwidth P0| Bitwidth P1|

+--------------------+----------+-------+---+----+------------+------------+

|tmp1_fu_177_p2 | + | 0| 0| 19| 19| 19|

|tmp_10_fu_277_p2 | + | 0| 0| 21| 21| 21|

|tmp_5_fu_241_p2 | + | 0| 0| 21| 21| 21|

|p_neg1_fu_325_p2 | - | 0| 0| 21| 1| 21|

|p_neg5_fu_300_p2 | - | 0| 0| 21| 1| 21|

|p_neg_t1_fu_344_p2 | - | 0| 0| 10| 1| 10|

|p_neg_t7_fu_319_p2 | - | 0| 0| 10| 1| 10|

|Cb_fu_378_p3 | Select | 0| 0| 10| 1| 1|

|Cr_fu_401_p3 | Select | 0| 0| 10| 1| 1|

|agg_result_Cb_V | Select | 0| 0| 8| 1| 2|

|agg_result_Cr_V | Select | 0| 0| 8| 1| 2|

|tmp_13_fu_372_p3 | Select | 0| 0| 10| 1| 10|

|tmp_s_fu_363_p3 | Select | 0| 0| 10| 1| 10|

|icmp1_fu_418_p2 | icmp | 0| 0| 2| 2| 1|

|icmp_fu_395_p2 | icmp | 0| 0| 2| 2| 1|

|tmp_14_fu_350_p2 | icmp | 0| 0| 26| 21| 13|

|tmp_15_fu_355_p2 | icmp | 0| 0| 26| 21| 13|

+--------------------+----------+-------+---+----+------------+------------+

|Total | | 0| 0| 235| 117| 177|

+--------------------+----------+-------+---+----+------------+------------+

* Multiplexer:

N/A

* Register:

+-------------------------------------+----+-----+-----------+

| Name | FF | Bits| Const Bits|

+-------------------------------------+----+-----+-----------+

|G_cast_reg_467 | 8| 20| 12|

|Y_reg_524 | 8| 8| 0|

|ap_CS_fsm | 1| 1| 0|

|ap_reg_ppiten_pp0_it1 | 1| 1| 0|

|ap_reg_ppiten_pp0_it2 | 1| 1| 0|

|ap_reg_ppiten_pp0_it3 | 1| 1| 0|

|ap_reg_ppiten_pp0_it4 | 1| 1| 0|

|ap_reg_ppiten_pp0_it5 | 1| 1| 0|

|ap_reg_ppiten_pp0_it6 | 1| 1| 0|

|ap_reg_ppstg_Y_reg_524_pp0_it5 | 8| 8| 0|

|ap_reg_ppstg_tmp_11_reg_540_pp0_it5 | 9| 9| 0|

|ap_reg_ppstg_tmp_12_reg_551_pp0_it5 | 1| 1| 0|

|ap_reg_ppstg_tmp_17_reg_556_pp0_it5 | 9| 9| 0|

|ap_reg_ppstg_tmp_4_reg_535_pp0_it5 | 1| 1| 0|

|p_neg_t1_reg_566 | 10| 10| 0|

|p_neg_t7_reg_561 | 10| 10| 0|

|s_B_V_read_reg_450 | 8| 8| 0|

|s_R_V_read_reg_456 | 8| 8| 0|

|tmp1_reg_509 | 19| 19| 0|

|tmp3_cast_reg_514 | 21| 21| 0|

|tmp5_cast_reg_519 | 21| 21| 0|

|tmp_10_reg_545 | 21| 21| 0|

|tmp_11_cast_reg_504 | 20| 20| 0|

|tmp_11_reg_540 | 9| 9| 0|

|tmp_12_reg_551 | 1| 1| 0|

|tmp_14_reg_571 | 1| 1| 0|

|tmp_15_reg_576 | 1| 1| 0|

|tmp_17_reg_556 | 9| 9| 0|

|tmp_2_reg_494 | 17| 17| 0|

|tmp_4_reg_535 | 1| 1| 0|

|tmp_5_reg_529 | 21| 21| 0|

|tmp_7_cast_reg_499 | 20| 20| 0|

|tmp_reg_489 | 18| 18| 0|

+-------------------------------------+----+-----+-----------+

|Total | 287| 299| 12|

+-------------------------------------+----+-----+-----------+

================================================================

== Interface

================================================================

* Summary:

+------------------------+-----+-----+------------+-----------------+--------------+

| RTL Ports | Dir | Bits| Protocol | Source Object | C Type |

+------------------------+-----+-----+------------+-----------------+--------------+

|ap_clk | in | 1| ap_ctrl_hs | rgb2ycbcr | return value |

|ap_rst | in | 1| ap_ctrl_hs | rgb2ycbcr | return value |

|ap_start | in | 1| ap_ctrl_hs | rgb2ycbcr | return value |

|ap_done | out | 1| ap_ctrl_hs | rgb2ycbcr | return value |

|ap_idle | out | 1| ap_ctrl_hs | rgb2ycbcr | return value |

|ap_ready | out | 1| ap_ctrl_hs | rgb2ycbcr | return value |

|agg_result_Y_V | out | 8| ap_vld | agg_result_Y_V | pointer |

|agg_result_Y_V_ap_vld | out | 1| ap_vld | agg_result_Y_V | pointer |

|agg_result_Cb_V | out | 8| ap_vld | agg_result_Cb_V | pointer |

|agg_result_Cb_V_ap_vld | out | 1| ap_vld | agg_result_Cb_V | pointer |

|agg_result_Cr_V | out | 8| ap_vld | agg_result_Cr_V | pointer |

|agg_result_Cr_V_ap_vld | out | 1| ap_vld | agg_result_Cr_V | pointer |

|s_R_V | in | 8| ap_none | s_R_V | scalar |

|s_G_V | in | 8| ap_none | s_G_V | scalar |

|s_B_V | in | 8| ap_none | s_B_V | scalar |

+------------------------+-----+-----+------------+-----------------+--------------+

データの流れとリソース。

パイプライン化され、1クロックで1個結果が出てくるようになりました。予想周波数は5.47[ns](約182MHz)。

この辺でいい加減一度ぐらいHDLシミュレーションしておかないと…いままでCのシミュレーションが楽で楽で…改めて思う…HDLのテストベンチってめんどくさい…

中身はほぼ同じで、BMPファイルを流し込んで結果を保存します。ただ、色々書くのが面倒なので、BGRをCbYCrに置き換えたBMPファイルだけ作成します。

ちなみにI/Oピンの情報はレポートファイルの一番下に書かれています。細かい制御方法はXilinxの資料にゆずりますが、今回はI/Oになにも指定していないので、関数の返値(YCbCr)に「ap_ctrl_hs」が、引数(RGB)に「ap_none」が設定されています。Y,Cb,Crそれぞれに「_ap_vld」という信号が付いてますが、この場合「ap_done」と同じ信号になるので見ません。

・「ap_rst」を解除する。

・「ap_start」を'1'にすると動作開始。

・クロック立ち上がり&「ap_ready」が'1'にだったら次のRGBデータをBMPファイルから与える。

・クロック立ち上がり&「ap_done」が'1'だったらYCbCrデータをBMPファイルに書き込む。

という制御だけになります。

`timescale 1ns / 1ps

`default_nettype none

//******************************************

//

module bmp_file;

integer bfSize; // File Size

integer bfOffBits; // Image Offset

integer biWidth; // Width

integer biHeight; // Height

integer biBitCount; // bit/pixel

integer imgsize; // Size

localparam headersize = 14+40;

reg [7:0] tch;

reg [7:0] header [0:headersize-1];

integer ifp, ofp, tx;

task init;

input [8*20:0] ifname;

input [8*20:0] ofname;

integer i;

begin

ifp = $fopen(ifname, "rb");

ofp = $fopen(ofname, "wb");

$display("open %s", ifname);

$display("%s created", ofname);

tx = $fread(header, ifp); //, 0, headersize);

$display("header = %d", tx);

bfSize = {header[ 5],header[ 4],header[ 3],header[ 2]};

bfOffBits = {header[13],header[12],header[11],header[10]};

biWidth = {header[21],header[20],header[19],header[18]};

biHeight = {header[25],header[24],header[23],header[22]};

biBitCount = {header[29],header[28]};

imgsize = bfSize - bfOffBits;

$display(" = %d,%x :(%d,%d,%d)",bfSize,bfOffBits,biWidth,biHeight,biBitCount);

for (i = 0; i < headersize; i = i+1) $fwrite(ofp,"%c",header[i]); // copy header info

end

endtask

task done;

begin

$fclose(ifp);

$fclose(ofp);

end

endtask

task sread;

output [7:0] B;

output [7:0] G;

output [7:0] R;

begin

$fread(B, ifp);

$fread(G, ifp);

$fread(R, ifp);

end

endtask

task swrite;

input [7:0] B;

input [7:0] G;

input [7:0] R;

begin

$fwrite(ofp,"%c", B);

$fwrite(ofp,"%c", G);

$fwrite(ofp,"%c", R);

end

endtask

endmodule

//

//******************************************

//******************************************

//

module tb;

localparam ifname = "../H-IIA-F13.bmp";

localparam ofname = "../out_hdl.bmp";

integer bfSize; // File Size

integer bfOffBits; // Image Offset

integer biWidth; // Width

integer biHeight; // Height

integer biBitCount; // bit/pixel

wire ap_start;

wire ap_done;

wire ap_idle;

wire ap_ready;

wire [7:0] agg_result_Y_V;

wire agg_result_Y_V_ap_vld;

wire [7:0] agg_result_Cb_V;

wire agg_result_Cb_V_ap_vld;

wire [7:0] agg_result_Cr_V;

wire agg_result_Cr_V_ap_vld;

wire [7:0] s_R_V;

wire [7:0] s_G_V;

wire [7:0] s_B_V;

reg clock;

reg reset;

reg start;

reg [7:0] R,G,B;

wire [7:0] Y,Cb,Cr;

rgb2ycbcr

tgt

(

.ap_clk (clock ), // ap_clk,

.ap_rst (reset ), // ap_rst,

.ap_start (ap_start ), // ap_start,

.ap_done (ap_done ), // ap_done,

.ap_idle (ap_idle ), // ap_idle,

.ap_ready (ap_ready ), // ap_ready,

.agg_result_Y_V (agg_result_Y_V ), // agg_result_Y_V,

.agg_result_Y_V_ap_vld (agg_result_Y_V_ap_vld ), // agg_result_Y_V_ap_vld,

.agg_result_Cb_V (agg_result_Cb_V ), // agg_result_Cb_V,

.agg_result_Cb_V_ap_vld (agg_result_Cb_V_ap_vld ), // agg_result_Cb_V_ap_vld,

.agg_result_Cr_V (agg_result_Cr_V ), // agg_result_Cr_V,

.agg_result_Cr_V_ap_vld (agg_result_Cr_V_ap_vld ), // agg_result_Cr_V_ap_vld,

.s_R_V (s_R_V ), // s_R_V,

.s_G_V (s_G_V ), // s_G_V,

.s_B_V (s_B_V ) // s_B_V,

);

bmp_file bmp();

assign ap_start = start;

assign s_R_V = R;

assign s_G_V = G;

assign s_B_V = B;

assign Y = agg_result_Y_V;

assign Cb = agg_result_Cb_V;

assign Cr = agg_result_Cr_V;

integer s,d;

initial

begin

reset <= 1'b1;

start <= 1'b0;

# 100;

@(posedge clock);

reset <= 1'b0;

@(posedge clock);

start <= 1'b1;

bmp.init(ifname,ofname);

for (s = 0; s < bmp.imgsize; s = s+3) begin

wait (ap_ready);

bmp.sread(B,G,R);

@(posedge clock);

end

start <= 1'b0;

# 500;

end

initial

begin

wait (start);

for (d = 0; d < bmp.imgsize; d = d+3) begin

wait (ap_done);

@(posedge clock);

bmp.swrite(Cb,Y,Cr);

end

bmp.done;

#300;

$stop;

end

// Clock

localparam period = (1000.0/148.5);

initial clock <= 1'b0;

always #(period/2) clock <= ~clock;

endmodule

//

//******************************************

`default_nettype wire

…行間から「HDLめんどくさい」が漏れてる…シミュレーションの最初と最後だけ出してみます。

カラーコードにしたので、シミュレーションの最後の値が動いていませんが、これで正常です。下の方のsとdがそれぞれのピクセルカウンタです。

HDLシミュレーションで生成されたBMPファイルと、Cの整数シミュレーションで生成されたBMPファイルのバイナリ比較は完全一致でした。Cの浮動小数点モデルで生成したBMPファイルとの比較では所々1bitの差が出ます。

PlanAheadでインプリしてみます。

Number of BUFGs 1 out of 32 3%

Number of DSP48E1s 7 out of 220 3%

Number of External IOBs 57 out of 200 28%

Number of LOCed IOBs 0 out of 57 0%

Number of Slices 102 out of 13300 1%

Number of Slice Registers 212 out of 106400 1%

Number used as Flip Flops 212

Number used as Latches 0

Number used as LatchThrus 0

Number of Slice LUTS 245 out of 53200 1%

Number of Slice LUT-Flip Flop pairs 307 out of 53200 1%

HLSの予測値にかなり近い値になりました。レポートされた周波数は150MHz制約に対してSlack 1.63[ns]、約198MHzという結果になってます。2013-04-24 22:56

nice!(0)

コメント(0)

トラックバック(0)

コメント 0