部品(リセットの同期化) [HDL]

共通で使ってる部品も残しておきます。

これは非同期リセットを同期化するモジュール。クロック1個に対して最低1つ実装します。クロックが止まっていてもリセットが入るように、リセットするときは非同期。リセット解除はクロック同期で、クロックとリセットがレーシングしないようにしてます。

パラメーターsrwはリセット解除後、何クロックリセットを維持するか、になります。2以上を設定します。

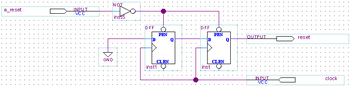

回路図追加。こういうのは図の方がわかりやすいですね。

リセット同期化

リセット同期化

ちなみに回路図入力にはQuartusII使ってます。もちろん実際に使うことは無いのですが、回路図の清書には便利です。

これは非同期リセットを同期化するモジュール。クロック1個に対して最低1つ実装します。クロックが止まっていてもリセットが入るように、リセットするときは非同期。リセット解除はクロック同期で、クロックとリセットがレーシングしないようにしてます。

パラメーターsrwはリセット解除後、何クロックリセットを維持するか、になります。2以上を設定します。

`timescale 1ns / 1ps

`default_nettype none

module sync_reset

#(

parameter srw = 2 // shift register width

)

(

input wire a_rst,

input wire clk,

output wire rst

);

reg [srw:1] rsr;

always @(posedge a_rst or posedge clk) begin

if (a_rst) rsr <= {srw{1'b1}}; // Async Reset

else rsr <= {rsr[srw-1:1],1'b0}; // Sync Reset Release

end

assign rst = rsr[srw];

endmodule

`default_nettype wirelibrary ieee;

use ieee.std_logic_1164.all;

entity sync_reset is

generic (

srw : integer := 2

);

port (

a_reset : in std_logic;

clock : in std_logic;

reset : out std_logic

);

end sync_reset;

architecture RTL of sync_reset is

signal rsr : std_logic_vector(1 to srw);

begin

process (clock, a_reset)

begin

if (a_reset = '1') then

rsr <= (others=>'1'); -- Async Reset

elsif (clock'event and clock = '1') then

rsr <= '0' & rsr(1 to srw-1); -- Sync Reset Release

end if;

end process;

reset <= rsr(srw);

end RTL; -- of sync_reset回路図追加。こういうのは図の方がわかりやすいですね。

リセット同期化

リセット同期化ちなみに回路図入力にはQuartusII使ってます。もちろん実際に使うことは無いのですが、回路図の清書には便利です。

2012-04-17 14:07

nice!(0)

コメント(0)

トラックバック(0)

コメント 0